|

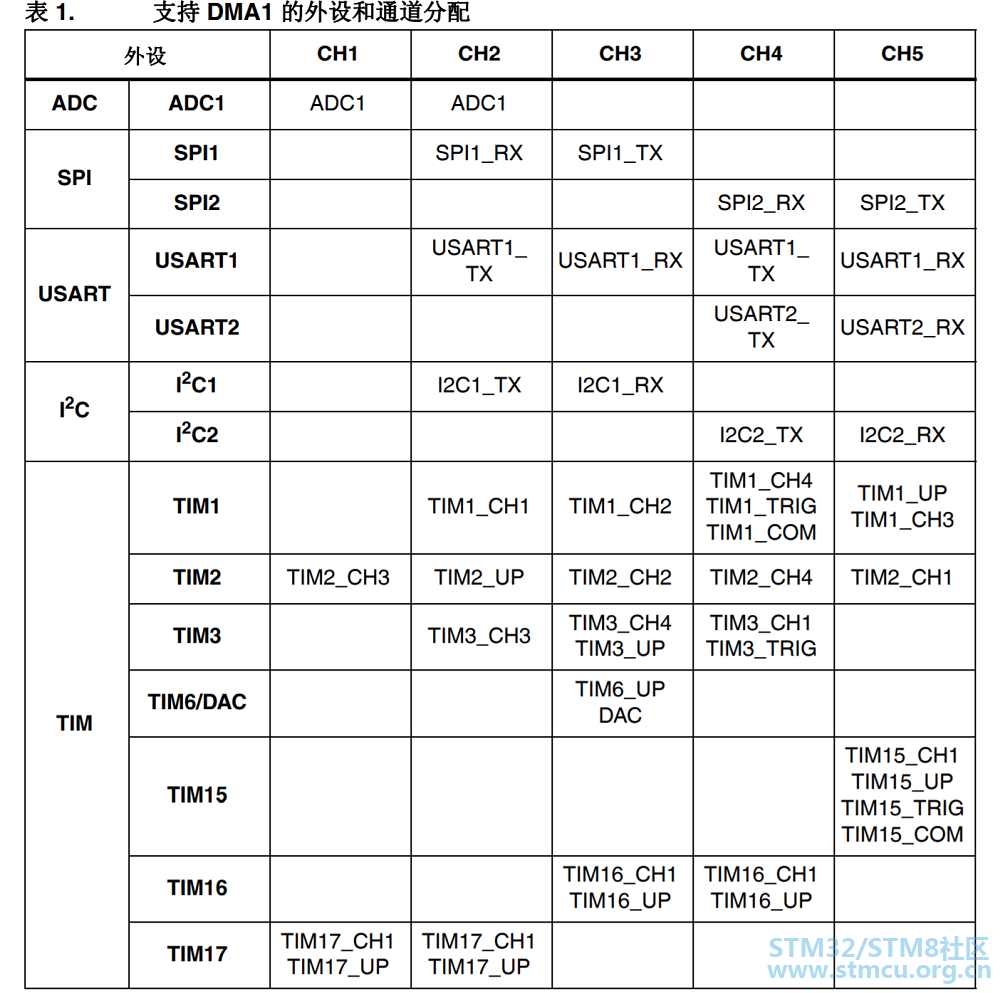

STM32F0xx的DMA控制器的使用- u: A) l8 m6 p w * @0 @# ?. A9 V% }1 e0 \4 f 前言 % M/ E& e$ D2 [. R# y& c 本应用笔记介绍了如何使用 STM32F0xx 直接存储器访问 (DMA) 控制器。STM32F0xx 的DMA 控制器、Cortex™-M0 内核、高级微控制器总线架构 (AMBA) 的总线和存储器系统为用户开发高数据带宽低延迟响应的软件提供了便利条件。 ' v' q- s J" x, a' ?& T' L T6 B- m 本应用笔记还介绍了如何充分利用这些特性以及确保不同的外设和子系统具有正确的响应时间。 $ ~! p) M/ r& ]5 i# H% J 注: 为确保用户快速入门,本文档介绍的应用示例均用 C 语言编程,这些示例位于STM32F0xx_StdPeriph_Lib 软件包内的 Project\STM32F0xx_StdPeriph_Examples 下$ {- c- r" B! r' u* ^0 A& H" @3 j 0 T& H! V$ X: u1 p' L 1 DMA 控制器说明 . Z2 v/ Q+ J% K0 p v 直接存储器访问 (DMA) 用于在外设与存储器之间以及存储器与存储器之间提供高速数据传输。可以在无需任何 CPU 操作的情况下通过 DMA 快速传输传输。这样节省的 CPU 资源可供其它操作使用。 DMA 允许在后台执行数据传输,无需 Cortex-M0 处理器干预。在此操作过程中,主处理器可以执行其它任务,仅当整个数据块需要处理时,才会中断主处理器。这样即使传输大量数据也不会对系统性能造成太大影响。 x: |! U b" k' Y% j3 P 3 O2 a( R3 d+ ?+ |/ m3 [ DMA 主要用于为不同的外设模块实现集中数据缓冲存储(通常在系统 SRAM 中)。与分布式解决方案(其中每个外设都需要实现自己的本地数据存储)相比,DMA 解决方案在硅片成本和功耗方面的成本较低。 $ h8 D0 S$ V* E5 y' n! s 根据使用的产品型号的不同,有一个或两个 DMA 模块。 % z4 g3 Q: D: @# L9 ?% ^" L) w . i7 U- \5 u9 @4 C STM32F0xx DMA 控制器总共有 5 个通道用于 DMA1,每个通道都专门管理来自一个或多个外设的存储器访问请求。它具有一个仲裁器,用于处理不同的 DMA 请求的优先级。4 Y) I" u: z6 \ & Z# s4 G T. z& O- I' h. J 1.1 DMA 概述 # _+ L; [5 \* g) G) P% X7 T DMA 主要特性: ● 可单独配置的通道(请求) 4 ?# L/ h' l9 j: r* f. y; I ● 每个通道都与专用的硬件 DMA 请求相连,同样每个通道上都支持软件触发 ● 来自一个 DMA 的通道的请求间的优先级可用软件编程(4 个级别:很高、高、中等、低),在软件优先级相同的情况下可以通过硬件决定优先级(例如,请求 1 的优先级高于请求 2) ● 独立的源和目标传输大小(字节、半字、字),模拟打包和解包。源和目标必须具有相同的数据大小(以通过数据大小对齐) ● 支持循环缓冲区管理 ) {& M1 P1 L! x8 { ● 3 个事件标志(DMA 半传输、DMA 传输完成和 DMA 传输错误),这 3 个事件标志逻辑或成为一个单独的中断请求 1 A1 Q3 m! h. L8 q9 b4 ` ● 存储器到存储器的传输 5 R2 J3 Z- E, S# }7 A1 e ● 外设到存储器和存储器到外设以及外设到外设的传输 % b. V4 _5 k& y) n( Y1 z5 y, \ ● FLASH、SRAM、APB 和 AHB 外设均可作为访问的源和目标 ● 可编程的数据传输数目:最大 65536 DMA 旨在为所有外设提供相对较大的数据缓冲区。此缓冲区通常位于系统 SRAM 中。 8 q, D5 o% Z8 a+ V4 w3 D, a# f ( m9 G5 j- ] l9 i! m7 f 每个通道都会在给定时间分配到一个唯一外设(数据通道)。连接到同一 DMA 通道(对于STM32F0xx 器件,为表 1 中的 CH1 到 CH5)的外设不能与使能的 DMA(DMA 功能在外设寄存器中处于使能状态)同时使用。 表 1 中显示了 STM32F0xx 器件中支持 DMA 传输的各种不同外设。

注: 有关详细信息,请参见 STM32F0xx 器件参考手册 RM0091 DMA 一节。 & X. d& W0 Z" f0 |6 X1.2 DMA 数据管理 % L) m8 Z4 z9 ?* \; f X" aDMA 控制器通过与 Cortex-M0 内核共用系统总线来执行直接存储器访问。当 CPU 与 DMA 具有相同的目标(存储器或外设)时,DMA 请求会暂停 CPU 访问系统总线达若干个周期,总线仲裁器执行循环调度,以确保 CPU 至少可以获得一半的系统总线带宽(存储器和外设)。 # ?3 R' t& Q7 @1.2.1 循环优先级方案 NVIC 和 Cortex-M0 处理器实施了延迟非常低的高性能中断方案。所有 Cortex-M0 指令均可在一个周期内执行,也可以按周期进行中断。为了在系统级保持这一优势,DMA 和总线矩阵可确保 DMA 不会长时间阻塞总线。循环优先级方案确保 CPU 可以根据需要每隔一个周期访问任意从总线一次。 1.2.2 外设到存储器、存储器到外设以及外设到外设的 DMA 传输 4 N" G! K# o1 q4 O5 L在发生一个事件后,外设向 DMA 控制器发送一个请求信号。DMA 控制器根据通道的优先权处理请求。当 DMA 控制器开始访问发出请求的外设时,DMA 控制器立即发送给它一个应答信号。当从 DMA 控制器得到应答信号时,外设立即释放它的请求。一旦外设释放了这个请求,DMA 控制器同时撤销应答信号。如果有更多的请求时,外设可以启动下一个周期。 每次 DMA 传输包含三个操作: + }8 s* S* T) r1 u7 c' Y● 从外设数据寄存器或者从当前外设/存储器地址寄存器指示的存储器地址取数据,第一次传输时的开始地址是 DMA_CPARx 或 DMA_CMARx 寄存器指定的外设基地址或存储器单元。 ● 向外设数据寄存器或者从当前外设/存储器地址寄存器指示的存储器地址存数据,第一次传输时的开始地址是 DMA_CPARx 或 DMA_CMARx 寄存器指定的外设基地址或存储器单元。 $ G* f( S) Y& \) n0 f! G5 v● 对 DMA_CNDTRx 寄存器执行一次递减操作,DMA_CNDTRx 寄存器存放着未完成的DMA 操作的计数。 ; o6 J$ k* n( ]$ o2 ?$ Q ]9 j3 a1.2.3 存储器到存储器的 4 r, p$ s( z& Z5 xDMA 传输DMA 通道的操作可以在没有外设请求的情况下进行。此模式称为“存储器到存储器”模式。如果 MEM2MEM 位置 1,则只要软件通过将使能位置 1 来使能通道,通道就会启动传输。DMA 计数器达到零后,传输结束。存储器到存储器模式不能与循环模式同时使用。 1.2.4 选择通道优先级 为了实现与外设之间的连续数据传输,相应的 DMA 通道必须能够维持足够的外设数据速率,并确保传输延迟的时间小于两个连续数据的间隔时间。 高速/高带宽外设必须具有最高的 DMA 优先级。符合外设最大数据延迟并且避免发生过载/欠载情况。 . D' P+ j0 l' E" ~$ c在带宽要求相同的情况下,建议为工作在从模式的外设(对数据传输速度没有控制权)分配的优先级高于工作在主模式的外设(可以控制数据流)。 默认情况下,对通道分配和硬件优先级(对于 STM32F0xx 器件,为 1 到 5)进行设置,以将最快的外设分配给优先级最高的通道。然而,对于某些应用来说,并不一定适合。在这种情况下,用户可以为每个通道配置一个软件优先级(4 个级别 —— 从“最高”到“低”),它将优先于硬件优先级。 |

| 点赞 |

STM32固件库分享,超全系列整理

三创电子(Tcreate)-STM32F030核心板代码

STM32F0 ADC(DMA中断)多通道,注释超详细

FreeRTOS在STM32F030上的移植

基于STM32移植而引发的疑问经验分享

分享STM32F051中文参考手册(重制书签版)

游名:STM32F0+Trinamic智能步进驱动芯片TMC5160(最高20A)参考原...

【MCU实战经验】+STM32F030的步进电机加减速

STM32F0的中文技术参考手册(标签处理过)

基于STM32F030硬件SPI经验分享