|

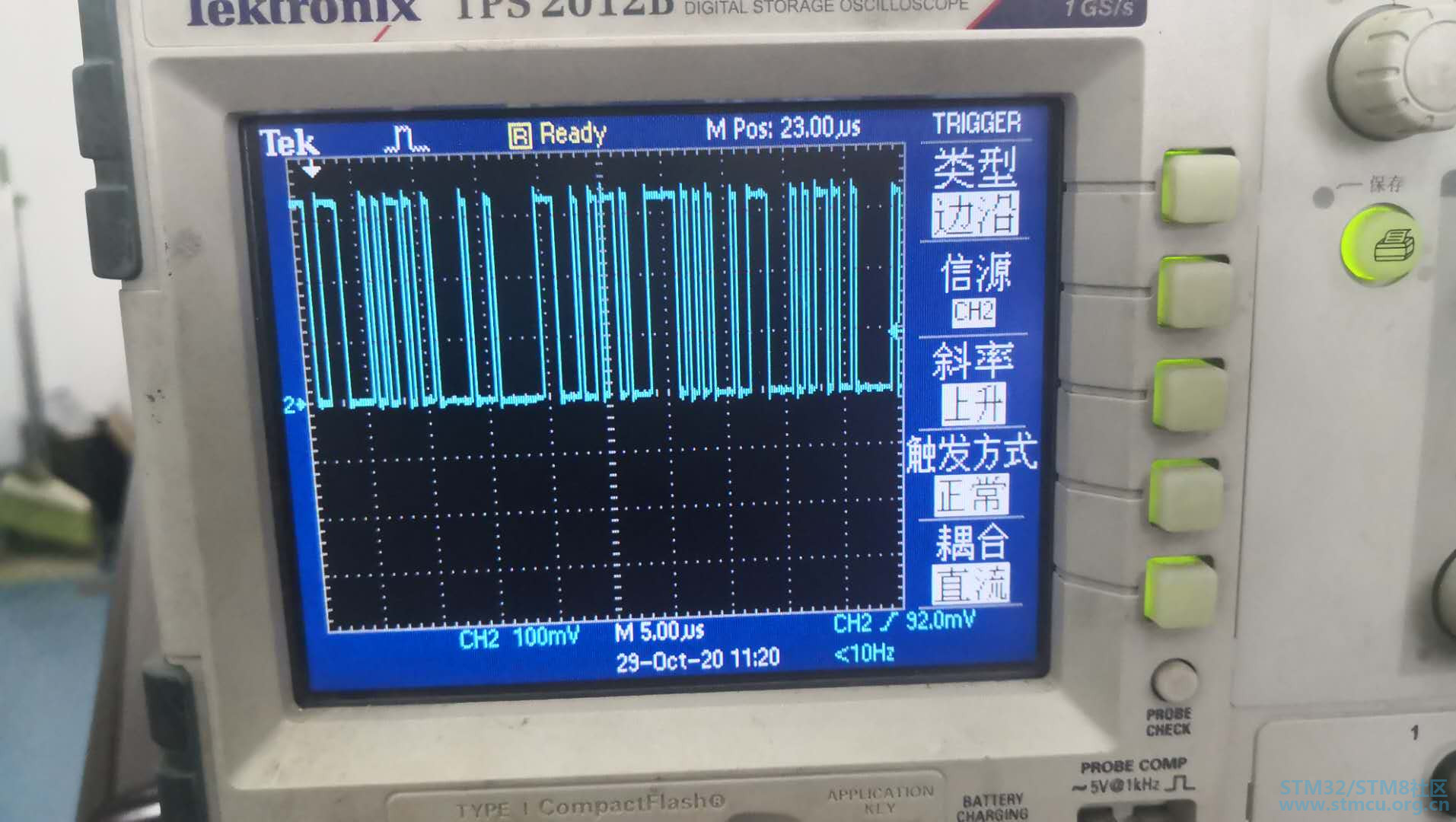

问题描述: STM32F103RCT6 使用SPI3与从设备通信时,烧写程序后板子自己运行SPI3的时钟正常(如图1),但是在MDK中使用debug功能调试时时钟不正常(如图2)。 自己运行时,只有接收到命令进行SPI3读写时会有时钟信号。而debug

dubugå¾æ

è¿è¡

å¾1

图1,烧写后,板子上电自己运行时SPI3的时钟 å¾2

图2,使用MDK的debug功能调试时点击,然后全速运行,SPI3的时钟。 但是,已配置端口复用,管教重映射关闭JTAG开启SWD。 RCC_APB2PeriphClockCmd(RCC_APB2Periph_AFIO,ENABLE); //使能复用功能 GPIO_PinRemapConfig(GPIO_Remap_SWJ_JTAGDisable,ENABLE); //重映射SWJ-JTAG 接口,开启SWD禁止JTAG 目前: 1、 整个程序运行的话有些逻辑不能正常工作,debug时不能正常工作很难进行调试。 2、 直接上电不debug运行,SPI3的通信有时正常有时不正常。 SPI部分程序: void SPI3_TemFPGA_Init(void) { SPI_InitTypeDef SPI_InitStructure; GPIO_InitTypeDef GPIO_InitStructure; /*Enable SPI2 and GPIO clocks */ RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOB | RCC_APB2Periph_GPIOA |RCC_APB2Periph_GPIOC , ENABLE);// RCC_APB1PeriphClockCmd(RCC_APB1Periph_SPI3,ENABLE); RCC_APB2PeriphClockCmd(RCC_APB2Periph_AFIO,ENABLE); //使能复用功能 // /*重映射SPI3*/ // GPIO_PinRemapConfig(GPIO_Remap_SPI3,ENABLE); GPIO_PinRemapConfig(GPIO_Remap_SWJ_JTAGDisable,ENABLE); //重映射SWJ-JTAG 接口,开启SWD禁止JTAG /*Configure SPI2 pins: SCK, MISO and MOSI */ GPIO_InitStructure.GPIO_Pin = SPI3_TemFPGA_PIN_SCK |SPI3_TemFPGA_PIN_MOSI; //|SPI3_TemFPGA_PIN_MISO; GPIO_InitStructure.GPIO_Mode= GPIO_Mode_AF_PP; GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz; GPIO_Init(SPI3_TemFPGA_GPIO, &GPIO_InitStructure); GPIO_InitStructure.GPIO_Pin= SPI3_TemFPGA_PIN_MISO ; GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IN_FLOATING; GPIO_Init(SPI3_TemFPGA_GPIO, &GPIO_InitStructure); /*Configure I/O for Flash Chip select */ GPIO_InitStructure.GPIO_Pin = SPI3_TemFPGA_CS; GPIO_InitStructure.GPIO_Mode = GPIO_Mode_Out_PP; GPIO_InitStructure.GPIO_Speed= GPIO_Speed_50MHz; GPIO_Init(SPI3_TemFPGA_CSGPIO, &GPIO_InitStructure); /*Deselect the FLASH: Chip Select high */ SPI3_TemFPGA_CS_HIGH(); // SPI3_TemFPGA_CS_LOW(); /*DRDY1 */ GPIO_InitStructure.GPIO_Pin = FPGA_AD1_DRDY_PIN ; GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IN_FLOATING; GPIO_Init(FPGA_AD1_DRDY_GPIO, &GPIO_InitStructure); /*DRDY2 */ GPIO_InitStructure.GPIO_Pin = FPGA_AD2_DRDY_PIN ; GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IN_FLOATING; GPIO_Init(FPGA_AD2_DRDY_GPIO, &GPIO_InitStructure); /* DRDY3 */ GPIO_InitStructure.GPIO_Pin = FPGA_AD3_DRDY_PIN ; GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IN_FLOATING; GPIO_Init(FPGA_AD3_DRDY_GPIO, &GPIO_InitStructure); /* CNT */ GPIO_InitStructure.GPIO_Pin = FPGA_CNT_DRDY_PIN ; GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IN_FLOATING; GPIO_Init(FPGA_CNT_DRDY_GPIO, &GPIO_InitStructure); SPI_I2S_DeInit(SPI3); /*SPI3 configuration */ SPI_InitStructure.SPI_Direction = SPI_Direction_2Lines_FullDuplex; SPI_InitStructure.SPI_Mode = SPI_Mode_Master; SPI_InitStructure.SPI_DataSize = SPI_DataSize_16b; SPI_InitStructure.SPI_CPOL = SPI_CPOL_Low; SPI_InitStructure.SPI_CPHA = SPI_CPHA_1Edge; SPI_InitStructure.SPI_NSS = SPI_NSS_Soft; SPI_InitStructure.SPI_BaudRatePrescaler = SPI_BaudRatePrescaler_32; SPI_InitStructure.SPI_FirstBit = SPI_FirstBit_MSB; SPI_InitStructure.SPI_CRCPolynomial = 7; SPI_Init(SPI3, &SPI_InitStructure); // SPI_SSOutputCmd(SPI3,ENABLE); /*Enable SPI1 */ SPI_Cmd(SPI3, ENABLE); } 头文件中的相关定义: /*********************************************************/ ///* Defines for the SPI and GPIO pins usedto drive the SPI Flash */ #define SPI3_TemFPGA SPI3 #define SPI3_TemFPGA_CLK RCC_APB1Periph_SPI3 #define SPI3_TemFPGA_GPIO GPIOB #define SPI3_TemFPGA_GPIO_CLK RCC_APB2Periph_GPIOB #define SPI3_TemFPGA_CSGPIO GPIOA #define SPI3_TemFPGA_CSGPIO_CLK RCC_APB2Periph_GPIOA #define SPI3_TemFPGA_CS GPIO_Pin_15 #define SPI3_TemFPGA_PIN_SCK GPIO_Pin_3 #define SPI3_TemFPGA_PIN_MISO GPIO_Pin_4 #define SPI3_TemFPGA_PIN_MOSI GPIO_Pin_5 /* Select SPI FLASH: Chip Select pinlow */ #define SPI3_TemFPGA_CS_LOW() GPIO_ResetBits(SPI3_TemFPGA_CSGPIO,SPI3_TemFPGA_CS) /* Deselect SPI FLASH: Chip Select pin high*/ #define SPI3_TemFPGA_CS_HIGH() GPIO_SetBits(SPI3_TemFPGA_CSGPIO,SPI3_TemFPGA_CS) #define FPGA_AD1_DRDY_PIN GPIO_Pin_6 #define FPGA_AD1_DRDY_GPIO GPIOC #define FPGA_AD1_DRDY_GPIO_CLK RCC_APB2Periph_GPIOC #define FPGA_AD2_DRDY_PIN GPIO_Pin_7 #define FPGA_AD2_DRDY_GPIO GPIOC #define FPGA_AD2_DRDY_GPIO_CLK RCC_APB2Periph_GPIOC #define FPGA_AD3_DRDY_PIN GPIO_Pin_8 #define FPGA_AD3_DRDY_GPIO GPIOC #define FPGA_AD3_DRDY_GPIO_CLK RCC_APB2Periph_GPIOC #define FPGA_CNT_DRDY_PIN GPIO_Pin_9 #define FPGA_CNT_DRDY_GPIO GPIOC #define FPGA_CNT_DRDY_GPIO_CLK RCC_APB2Periph_GPIOC #define ReadAD1DRDYState() GPIO_ReadInputDataBit(FPGA_AD1_DRDY_GPIO,FPGA_AD1_DRDY_PIN) #define ReadAD2DRDYState() GPIO_ReadInputDataBit(FPGA_AD2_DRDY_GPIO, FPGA_AD2_DRDY_PIN) #define ReadAD3DRDYState() GPIO_ReadInputDataBit(FPGA_AD3_DRDY_GPIO, FPGA_AD3_DRDY_PIN) #define ReadCNTDRDYState() GPIO_ReadInputDataBit(FPGA_CNT_DRDY_GPIO,FPGA_CNT_DRDY_PIN) |

自己画的STM32F103RCT6的板子下载识别不到芯片。

adc采集电压

STM32 CAN通讯收发异常

STM32硬件IIC

STM32IDE工程内如何访问、计算得到当前程序flash已经使用的情况?

数据丢失

STM32F107RBT6 页擦除函数返回值成功但目标扇区数据并未擦除

L6235Q驱动MAXON三相无刷直流电机,FWD引脚接入PWM波,占空比50%的时候电机不转动,其他占空比电机转动,数据手册并没提及,请问有什么依据吗?

板子肯定没问题,用cubeprogrammer烧录报错

STM32F103ZET6 CS信号无法拉高