|

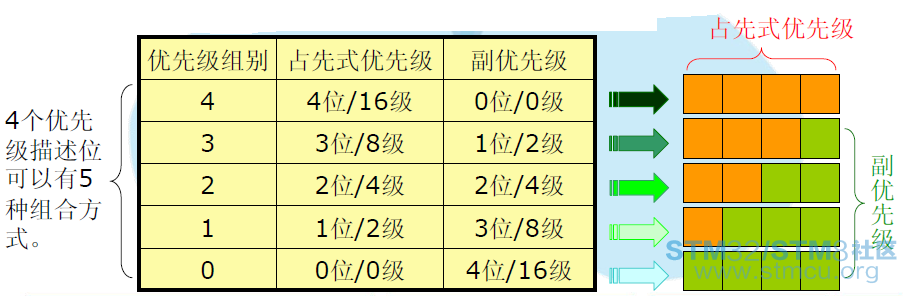

1:STM32中断优先级: 01:占先式优先级(pre-emption priority)' [, X! D: l8 `+ Z: E$ o8 H( E7 n 高占先式优先级的中断事件会打断当前的主程序/中断程序运行——抢断式优先响应,俗称中断嵌套。 02:副优先级(subpriority)2 v9 g2 i: Z* I, ~5 q2 d 在占先式优先级相同的情况下,高副优先级的中断优先被响应; 在占先式优先级相同的情况下,如果有低副优先级中断正在执行,高副优先级的中断要等待已被响应的低副优先级中断执行结束后才能得到响应——非抢断式响应(不能嵌套)。7 w* ~, @6 D, |/ i+ ^ 03:判断中断是否会被响应的依据 首先是占先式优先级,其次是副优先级;4 Y& M# O0 S3 i8 B% m! c7 O 占先式优先级决定是否会有中断嵌套;/ T- C/ }2 D% r. p% z Reset、NMI、Hard Fault 优先级为负(高于普通中断优先级)且不可调整。3 x' A; v" j- Q% c3 {) v! a% {' F8 k 2:STM32中断优先级配置! l" B; C6 M% \5 A! {( m3 f& o 每一个中断都有一个专门的寄存器(Interrupt Priority Registers)来描述该中断的占先式优先级及副优先级。在这个寄存器中STM32使用4个二进制位描述优先级(Cortex-M3定义了8位,但STM32只使用了4位)。" J/ w" v$ c: ~# U, f 占先式优先级与副优先级的分配4个描述优先级位有下列5种组合使用方式。“优先级组别”决定如何解释这4位。1 i3 ~7 f0 k; R. @1 X

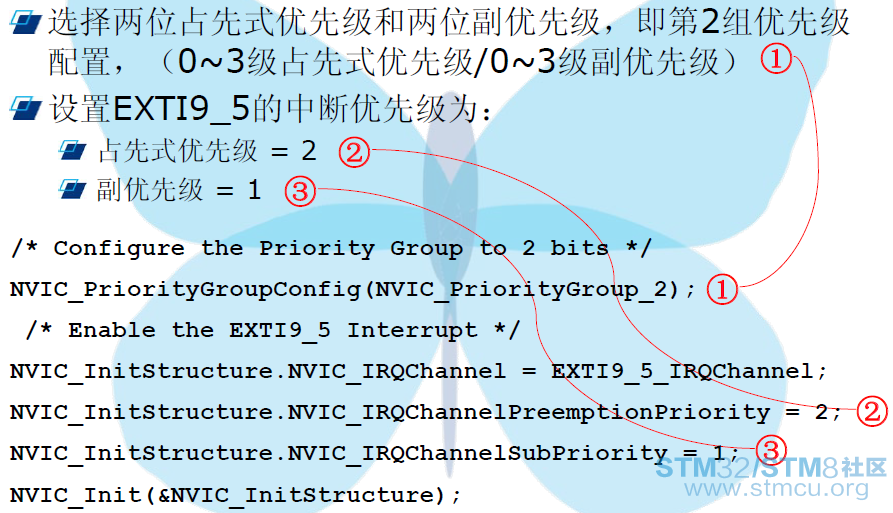

+ H) ~$ \, b* U( q) d: N0 @ 3:STM32中断优先级配置示例

4:STM32总中断控制 void __disable_irq(void) // DisableInterrupts 关总中断 void __enable_irq(void) // EnableInterrupts 开总中断 更多精彩内容请关注微信公众号,一起学习一起进步。 或扫码关注

# {0 B3 h( p' c2 H 5 |9 C0 H3 Y- m7 m8 X7 \ |