1、综述( [& x1 ]5 B/ D; H9 v- n1 x

0 v7 }: ?' Q& ~4 X6 Y% f1 |DMA(Direct memory access)直接内存访问,被用于内存和内存之间或内存和外设之间的高速数据传输。数据传输可以在没有CPU的干预下快速移动,这样可以保持CPU资源处理其他事情。

7 A C, S6 b3 H! V5 T6 v

DMA 控制器基于复杂的总线矩阵架构,将功能强大的双 AHB 主总线架构与独立的 FIFO 结合在一起,优化了系统带宽,下图①处,可以看出双 AHB 主总线架构与独立的 FIFO的结构。

" }% @' M" h- u' k! a; j8 y* x, {5 ]4 q, {

, Y$ p6 Y4 {; d* `: F; i注意看英文备注: 9 \* m* i X; E$ }6 r1 d

DMA1控制器AHB外设端口没有像DMA2一样连接到总线矩阵,所以只有DMA2数据流可以执行存储器到存储器的传输。 * O5 [7 Y: O) ^9 n# n% D

我们对上图的②处,(DMA1和DMA2结构一样,我们就选择DMA1)详细看

, k' J( S$ L: ]0 j6 e; q

9 p. g; O, B. a; x6 A: h D①每个数据流总共可以有多达 8 个通道(或称请求)。 # r/ O E. l* ]# I0 S/ C

②DMA1共有8个数据数据流(两个DMA共有16个数据流)。

0 U4 R/ ? S' q9 X" Q

③每个DMA都有数据流仲裁器,用于处理 DMA 请求间的优先级。 / d+ R' J& z* g; C' ]$ a T

④DMA的数据流又有独立的FIFO。

8 ~) `% X% J) M/ I# u/ P

⑤DMA采用双 AHB 主总线架构。

8 c& k( K/ s) c# K8 b% c: L8 Z

备注: + K9 {) ^! ^! N* Y' `6 X/ M

①处是选择器,配置完成只能选择一个通道,而③处是仲裁器,也就是说,配置完成,可能8个数据流全部存在,由仲裁器判断优先级。 / L2 v& J1 m+ ~# j: j

4 _# ^( s3 D& p9 z, D6 _ ^2、DMA事务0 c- n. g& P; r0 q' o6 o: I3 r2 _5 ^

DMA从传输事务包含一系列的给定数目的数据传输序列。传输的数目可以通过软件编程,8位,16位或32位。

% {2 I7 B4 t( r+ _- M

每一次DMA传输包含3个操作 6 c D- `3 H, K, r5 u9 W

通过 DMA_SxPAR 或 DMA_SxM0AR 寄存器寻址,从外设数据寄存器或存储器单元中加载数据。 通过 DMA_SxPAR 或 DMA_SxM0AR 寄存器寻址,将加载的数据存储到外设数据寄存器或存储器单元。 ·DMA_SxNDTR 计数器在数据存储结束后递减,该计数器中包含仍需执行的事务数。

" r8 [ Q6 }2 F+ U 2 g; k: Q! Y. }; D

, P/ ] F3 \2 n) ?) |+ [. l

在产生事件后,外设会向 DMA 控制器发送请求信号。DMA 控制器根据通道优先级处理该请求。只要 DMA 控制器访问外设, DMA 控制器就会向外设发送确认信号。外设获得 DMA 控制器的确认信号后,便会立即释放其请求。一旦外设使请求失效, DMA 控制器就会释放确认信号。如果有更多请求,外设可以启动下一个事务。8 \. I/ l3 u$ {: x' Z: d3 z

6 m3 Y& f' q+ \3、通道选择

) I) ^2 a) c+ c- d8 R0 _ o& V" X; d9 t! S2 J

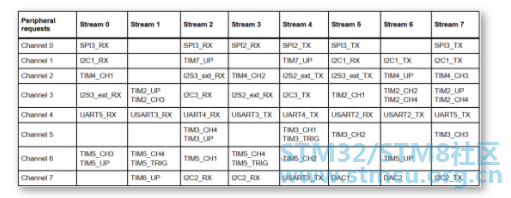

每个数据流可以有8个通道。

{ C, w7 D1 \& T6 v& A& i1 e" R通过上图①可以看出,通道选择仲裁器可以通过DMA_SxCR寄存器的CHSEL[2:0]配置

5 a8 [, j8 n& z0 q7 I4 j

DMA的请求可以来自TIM,ADC,SPI等外设。

5 w% a0 l4 c, a. x/ F- _

DMA1的请求通道 ) H$ t1 f8 F2 W$ t* B* o

DMA2的请求通道

2 `3 L0 r- R$ Q

9 t/ ?9 S2 m( Y' ? p$ O+ L- E. @/ C) C; y# _

4、仲裁器

2 L/ N" i2 ^; r3 w

, u: C8 d2 ?& y% E& n9 @! B6 N仲裁器为两个 AHB 主端口(存储器和外设端口)提供基于请求优先级的 8 个 DMA 数据流请求管理,并启动外设/存储器访问序列。

; n. i4 Z: {) d: c8 U7 }& |( s J* U

优先级管理分为两个阶段 " \6 }( \+ p5 E1 I

b( ~3 N4 O: X; g4 |. e

0 p7 X/ Q) C2 Q2 M; J4 d+ O5、DMA数据流

/ b0 w& p W+ J z

- f7 Y* c3 j' } a8个DMA控制器数据流都能够提供源和目标之间的单向传输链路。 ! Y2 ?1 w+ d& B! r! x

每个数据流配置后都可以执行

' a& D% `/ E( v/ T& F

要传输的数据量(多达 65535)可以编程,并与连接到外设 AHB 端口的外设(请求 DMA 传输)的源宽度相关。每个事务完成后,包含要传输的数据项总量的寄存器都会递减。 $ c" C: Z8 v5 [' \' { I7 E3 ]9 f

; Z1 `$ _/ u5 {9 A2 K7 h6、源、目标和传输模式 `" f/ K' |3 h6 F! P# }0 U/ Z

源地址和目标地址可以在整个4G地址空间,在0x00000000和0xFFFFFFFF之间。

2 [9 o8 Q3 m7 c5 J

在DNA_SxCR寄存求的DIR[1:0]配置DMA的传输方式。 3 y5 t, d5 z3 b; x g+ I

源地址和目标地址的关系 当数据宽度是半字或字时,外设地址或存储器地址必须是半字或字对齐

6 A |' b# b9 j. h* N0 P* V5 T

6.1、外设到存储器模式 当配置成外设到存储器的DMA传输模式时,两种模式 ' b- _1 `9 A% m" V% q7 A; V- d) x

; p( _2 z0 N) O2 H0 [传输开始条件,使能数据流(DMA_SxCR 寄存器中的位 EN 置 1),然后外设发出请求,再然后该请求赢得了数据流仲裁,才会开始传输。

Q+ V7 x: ?6 J% Q0 A

传输停止条件,下列满足一条即可

; N- T* k: |& |. N: r; B3 _

6.2 存储器到外设模式.

5 }" v; P) ~$ sFIFO模式 这种模式,只要使能数据流(DMA_SxCR 寄存器中的位 EN 置 1),存储器数据就会传输到FIFO中,发生外设请求,FIFO数据会移出并存储到目标地址。当FIFO小于阈值,存储器的数据会重载FIFO。 1 \ f( ^: I2 `; _% f

直连模式 使能数据流时,DMA传输存储器的第一个数据到内部FIFO,发生外设请求时,DMA把预装在值发送的目标地址,然后进行下一个数据的传输。预装载的数据大小为 DMA_SxCR 寄存器中 PSIZE 位字段的值。 / `7 C, E* ]( J1 s

传输停止条件,下列满足一条即可

9 y: `0 S, F$ _+ h

存储器到外设模式和外设到存储器模式一样,同样需要对应数据流赢得仲裁,才会启动传输 6 k+ s8 B2 f. C" g5 l0 R

4 L4 q1 g1 \; O! V* P6.3 存储器到存储器模式 这种模式较为简单,没有外设请求

1 R. I3 A6 }4 M# h9 J* u$ u

启动传输 0 V: K$ c, h. P( b7 q0 j% h/ v+ }

DMA_SxCR 寄存器中的使能位 (EN) 置 1 来使能数据流时,数据就会从源地址传输到FIFO,到达FIFO阈值时,FIFO数据移出到目标地址。

. x$ n$ m0 E* k% w2 X& L

停止传输,下列满足一条即可 当然,同样该数据流需要赢得仲裁。 ; Q3 G9 c/ a# T' R6 Z8 b0 l* P

& e1 ?: ^3 o( `3 k6 o& A& A. A

4 S. `- I1 W) e) M6 r I: }

7、指针递增7 n, l8 ?5 I7 x% C# w

6 l9 Y" Z5 q& I# A% K

外设和存储器指针在每次传输后自动向后递增或保持常量,根据DMA_SxCR寄存器的PINC和MINC位。 ' C4 m" ^/ m; E7 G s, \

禁止递增模式时非常有用的,当外设源和目标数据是通过单个寄存器访问的。

( s2 E9 C9 T, @8 Y# K8 j

如果使能了递增模式,则根据在 DMA_SxCR 寄存器 PSIZE 或 MSIZE 位中编程的数据宽度,下一次传输的地址将是前一次传输的地址递增 1(对于字节)、 2(对于半字)或 4(对于字)。 2 G: E% c' H3 a( ~/ N

为了优化封装操作,可以不管 AHB 外设端口上传输的数据的大小,将外设地址的增量偏移大小固定下来。DMA_SxCR 寄存器中的 PINCOS 位用于将增量偏移大小与外设 AHB 端口或32 位地址(此时地址递增 4)上的数据大小对齐。PINCOS 位仅对 AHB 外设端口有影响。 ( L" W; E7 e* P" M5 X" {

如果将 PINCOS 位置 1,则不论 PSIZE 值是多少,下一次传输的地址总是前一次传输的地址递增 4(自动与 32 位地址对齐) 。但是, AHB 存储器端口不受此操作影响。

* D9 F* c' m5 Z; k0 Q3 S" b: Z& g+ ]

如果 AHB 外设端口或 AHB 存储器端口分别请求突发事务,为了满足 AMBA 协议(在固定地址模式下不允许突发事务),则需要将 PINC 或 MINC 位置 1。

% X4 _) w' L' i. ~5 ?

9 N0 M2 q# ]6 S3 ^+ J& |8 r8、循环模式

0 }9 N- s2 H. K/ M+ k, p" t, Z+ E' _* r, h

循环模式可用于处理循环缓冲区和连续数据流(例如 ADC 扫描模式)。可以使用 DMA_SxCR 寄存器中的 CIRC 位使能此特性。 当激活循环模式时,要传输的数据项的数目在数据流配置阶段自动用设置的初始值进行加载,并继续响应 DMA 请求。

! f% i( ^7 N) ^0 @( M1 m( {

也就是说,比如我们要从内存中采集 64 个字节发送到串口,如果设置为重复采集,那么它会在 64 个字节采集完成之后继续从内存的第一个地址采集,如此循环。这里我们设置为一次连续采集完成之后不循环。所以设置值为 DMA_Mode_Normal。在我们下面的实验中,如果设置此参数为循环采集,那么你会看到串口不停的打印数据,不会中断。

A3 V- z. ^& F+ a2 k9 d

" }0 C$ u0 w! n* s ^/ J( n, \1 i- [1 S( V( h8 c

9、双缓冲模式9 h& p3 z3 K: O' }/ a

2 ^! b( m; m' D, o( i5 B' J/ p

此模式可用于所有 DMA1 和 DMA2 数据流。 5 [9 h- a* W9 P& P4 ?

通过将 DMA_SxCR 寄存器中的 DBM 位置 1,即可使能双缓冲区模式。

1 J5 O* s" f$ z7 r

除了有两个存储器指针之外,双缓冲区数据流的工作方式与常规(单缓冲区)数据流的一样。使能双缓冲区模式时,将自动使能循环模式( DMA_SxCR 中的 CIRC 位的状态是“无关”),并在每次事务结束时交换存储器指针。 ) b# R) H) [; s; C+ d' h% u

在此模式下,每次事务结束时, DMA 控制器都从一个存储器目标交换为另一个存储器目标。这样,软件在处理一个存储器区域的同时, DMA 传输还可以填充/使用第二个存储器区域。

$ W r! V V1 q

基于DMA双缓冲模式的的特点,应用中必须开辟两个存储区以及存放两个存储区首地址的存储寄存器,DMA_SxM0AR和DMA_SxM1AR。 ) V1 X4 u5 h: c

1:DMA_SxM0AR:指向存储区0(DMA_Memory_0),单缓冲模式下默认使用该寄存器做存储区指针。 ( d6 c2 k* y# r

2:DMA_SxM1AR:指向存储区1(DMA_Memory_1),仅在DMA双缓冲模式下才能使用。 0 G; O. R1 t! C$ h" k

3:DMA正在访问的当前存储区由DMA_SxCR表示 CT:当前目标 CT = 0:DMA正在访问存储区0,CPU可以访问存储区1。 CT = 1:DMA正在访问存储区1,CPU可以访问存储区0。

2 M' q3 ^! x5 f

优点:

% i* O/ }( i4 S

使用DMA双缓冲传输,既可以减少CPU的负荷,又能最大程度地实现DMA数据传输和CPU数据处理互不打扰又互不耽搁,DMA双缓冲模式的循环特性,使用它对存储区的空间容量要求也会大大降低。尤其在大批量数据传送时,你只需开辟两个合适大小的存储区,能满足DMA在切换存储区时的当前新存储区空出来就好,并不一定要开辟多大多深的存储空间,单纯一味地加大双缓冲区的深度并不明显改善数据传输状况。

( p+ u7 K: V4 l

2 a8 U. u( i+ @5 T+ X* ?

) t a+ x5 Q) Y& D, l# c" B10、代码

* ]* V1 _: J$ H k

7 Q: ^- B- y% o' z/ D+ _

% h# ?; ~2 u6 }- X! F7 f9 p* F+ G9 i$ l- \5 S0 T' L v

标准外设库配置代码:

5 r" P) w, ^, Z' p; P0 U- /* Configure DMA Stream */

: V P0 a, A8 d4 o& I - DMA_InitStructure.DMA_Channel = DMA_Channel_0;2 N+ G5 I" ?3 @- O- ~- ~, \

- DMA_InitStructure.DMA_PeripheralBaseAddr = (uint32_t)SRC_Const_Buffer;

9 N& v! A7 V3 w# U7 C3 O: ~ - DMA_InitStructure.DMA_Memory0BaseAddr = (uint32_t)DST_Buffer;9 B1 ` K7 v. ?1 V7 Z' {* q( f

- DMA_InitStructure.DMA_DIR = DMA_DIR_MemoryToMemory;

7 ?: _' c5 w/ F3 ~ - DMA_InitStructure.DMA_BufferSize = (uint32_t)32;6 i6 X8 g! f! h7 R

- DMA_InitStructure.DMA_PeripheralInc = DMA_PeripheralInc_Enable;

5 J2 _0 \5 z e0 N3 j! ~0 z - DMA_InitStructure.DMA_MemoryInc = DMA_MemoryInc_Enable;( s7 P& I! R" b2 H

- DMA_InitStructure.DMA_PeripheralDataSize = DMA_PeripheralDataSize_Word;8 d( X7 D* h/ {( n

- DMA_InitStructure.DMA_MemoryDataSize = DMA_MemoryDataSize_Word;

$ r" C1 i& y$ W; y7 m5 j - DMA_InitStructure.DMA_Mode = DMA_Mode_Normal;

& b0 T. D( K1 p& A" W4 J0 O - DMA_InitStructure.DMA_Priority = DMA_Priority_High;5 w9 H, R) c* k3 H' a% [: i

- DMA_InitStructure.DMA_FIFOMode = DMA_FIFOMode_Disable;.

& u- J1 C1 a% h4 }8 M( K! y) m$ e - DMA_InitStructure.DMA_FIFOThreshold = DMA_FIFOThreshold_Full;

% ~1 l* z+ ~6 R$ p7 \% g - DMA_InitStructure.DMA_MemoryBurst = DMA_MemoryBurst_Single;2 I7 W& R6 M, l& v% B3 ^: j

- DMA_InitStructure.DMA_PeripheralBurst = DMA_PeripheralBurst_Single;

. `, b) s+ Z( y9 ~* ^ - DMA_Init(DMA2_Stream0, &DMA_InitStructure);

0 x% I" w" ]! h) o MDMA_Channel : 设置 DMA 数据流对应的通道,供每个数据流选择的通道请求多达 8 个,取值有 - 6 U, G: _/ w Y$ n% g G" J8 ]

- #define DMA_Channel_0 ((uint32_t)0x00000000), \' r8 Z+ K( y4 l8 H& F

- #define DMA_Channel_1 ((uint32_t)0x02000000)5 j# M( @( {& S4 l6 D

- #define DMA_Channel_2 ((uint32_t)0x04000000)+ z2 S7 [6 a% T" `7 |) _2 h- l+ }

- #define DMA_Channel_3 ((uint32_t)0x06000000)

! b% H# p1 L4 c- U7 R - #define DMA_Channel_4 ((uint32_t)0x08000000)/ ^0 U: ]- g% N

- #define DMA_Channel_5 ((uint32_t)0x0A000000)

7 f' o ` u# k/ ` - #define DMA_Channel_6 ((uint32_t)0x0C000000)

. g* a; q% z3 v2 M: u# T - #define DMA_Channel_7 ((uint32_t)0x0E000000)

) `. O0 o% Y3 z8 G/ w - DMA_PeripheralBaseAddr :

DMA_PeripheralBaseAddr : DMA 传输的外设基地址,假设进行uart1串口DMA 传输,我们可以按照寄存器的地址偏移直接设置地址:0x40011004,也可以直接使用ST提供库的表示方法:&USART1->DR。 / p8 s( ~: q; F. V8 [

DMA_Memory0BaseAddr : DMA 传输的内存基地址。 DMA_DIR: 设置数据传输方向,有存储器到存储器,存储器到外设,外设到存储器三种选择,取值有:

; \4 K' F1 ~: j* x& q1 t; k1 L( Y- #define DMA_DIR_PeripheralToMemory ((uint32_t)0x00000000); V. N6 u5 [; |1 E, Y0 N

- #define DMA_DIR_MemoryToPeripheral ((uint32_t)0x00000040) 6 `3 C' \7 c* T3 l

- #define DMA_DIR_MemoryToMemory ((uint32_t)0x00000080)

DMA_BufferSize: 设置一次传输数据量的大小 ( l8 ~: l# T9 k+ P- I x8 O

DMA_PeripheralInc: 设置传输数据的时候外设地址是不变还是递增,如果设置为递增,那么下一次传输的时候地址加 1,取值有: - 值有:6 M& J) ?% @0 _6 p7 Z

2 j: [! ?/ N2 f- #define DMA_PeripheralInc_Enable ((uint32_t)0x00000200). q2 P# ~) K5 U1 Q/ m

- #define DMA_PeripheralInc_Disable ((uint32_t)0x00000000)

* O8 f/ k; j% O. F3 Z/ F* l# R+ i# cDMA_MemoryInc: 设置传输数据时 候内存地址 是否递增。这个参数和DMA_PeripheralInc 意思接近,只不过针对的是内存(存储器),取值有:

+ F1 ^) u! [7 e$ t' J0 _1 m

; q+ T& U8 ^8 j4 G- #define DMA_MemoryInc_Enable ((uint32_t)0x00000400) 5 N% E9 R3 I4 R& g8 c8 Y

- #define DMA_MemoryInc_Disable ((uint32_t)0x00000000)

DMA_PeripheralDataSize: 设置外设的数据长度是为字节传输(8bits),半字 传 输 (16bits) 还 是 字 传 输 (32bits),取值有:

0 V; L0 |' ~* U8 Y6 C

- #define DMA_PeripheralDataSize_Byte ((uint32_t)0x00000000)

8 I! u( Z* r9 J - #define DMA_PeripheralDataSize_HalfWord ((uint32_t)0x00000800)

8 Q+ [( S* Z0 a8 i* d1 @& J - #define DMA_PeripheralDataSize_Word ((uint32_t)0x00001000)

DMA_MemoryDataSize: 用来设置内存的数据长度。 $ F' M! J4 q" F

DMA_Mode: 设置 DMA 模式是否循环采集,取值有:

" P# }" w2 l6 b

- 5 x6 j0 i+ f4 e+ l8 M2 q

- #define DMA_Mode_Normal ((uint32_t)0x00000000)

& z! z2 i0 \# _! j - #define DMA_Mode_Circular ((uint32_t)0x00000100)

DMA_Priority: 设置 DMA 通道的优先级,有低,中,高,超高三种模式。就是仲裁器仲裁的时候用的,当多个数据流同时开启,DMA仲裁器优先处理优先级高的数据流,取值有:

- w3 x% A! k2 N5 T

- #define DMA_Priority_Low ((uint32_t)0x00000000) ! t, @! g3 ?0 Z& z/ J

- #define DMA_Priority_Medium ((uint32_t)0x00010000)

; i) K7 p3 P1 ^7 R1 _ - #define DMA_Priority_High ((uint32_t)0x00020000)

6 t2 S, [/ @0 B/ e - #define DMA_Priority_VeryHigh ((uint32_t)0x00030000)

DMA_FIFOMode: 设置是否开启 FIFO 模式,取值有: - #define DMA_FIFOMode_Disable ((uint32_t)0x00000000) 3 B, d* B" \( `7 e

- #define DMA_FIFOMode_Enable ((uint32_t)0x00000004)

DMA_FIFOThreshold: 选择 FIFO 阈值,只有上个参数选择使能FIFO,这个参数才有用。取值有:

' b$ Q$ L6 e' k8 S% Z$ L) \

- #define DMA_FIFOThreshold_1QuarterFull ((uint32_t)0x00000000)' X) T: O1 b8 m" M W

- #define DMA_FIFOThreshold_HalfFull ((uint32_t)0x00000001)

; V E' \# Y* ^ - #define DMA_FIFOThreshold_3QuartersFull ((uint32_t)0x00000002)

~* `# L% |+ {( o- ], a% b - #define DMA_FIFOThreshold_Full ((uint32_t)0x00000003)

DMA_MemoryBurst: 配置存储器突发传输配置。可以选择为 4 个节拍的增量突发传输 ,8 个节拍的增量突发传输 , 16 个街拍的增量突发传输以及单次传输。取值有: " j* e' S/ O" a( A8 {' q" m

- 9 `, m" W; K. w7 s

- #define DMA_MemoryBurst_Single ((uint32_t)0x00000000) & ^1 J3 D3 N+ C$ M

- #define DMA_MemoryBurst_INC4 ((uint32_t)0x00800000) 9 @" \9 C% P* N# m. z5 e

- #define DMA_MemoryBurst_INC8 ((uint32_t)0x01000000) " y% |6 A+ s2 r! ~$ ~

- #define DMA_MemoryBurst_INC16 ((uint32_t)0x01800000)

DMA_PeripheralBurst: 配置外设突发传输配置。跟前面一个参数DMA_MemoryBurst 作用类似,只不过一个针对的是存储器。取值有

" D6 q# Y# K: u3 v$ C3 T2 z) d3 y

- #define DMA_PeripheralBurst_Single ((uint32_t)0x00000000) % R4 m9 w; o/ n9 `2 y

- #define DMA_PeripheralBurst_INC4 ((uint32_t)0x00200000)

$ m' L4 ]0 X, Z% Y& P! K+ N3 I) @ - #define DMA_PeripheralBurst_INC8 ((uint32_t)0x00400000)

6 M8 o9 {- {: w& I- k/ Q; B - #define DMA_PeripheralBurst_INC16 ((uint32_t)0x00600000)

|