|

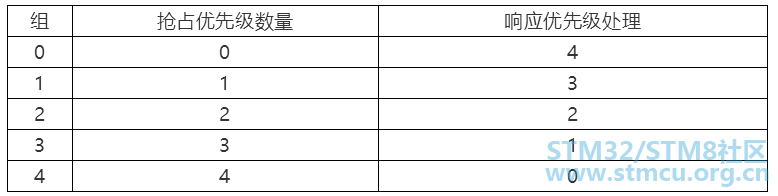

STM32学习笔记03—中断架构 ; g: m: c m/ }( Z2 @ 3.1 STM32F103中断概述; U8 D0 H+ w. W7 X2 r: t Cortex-M3内核支持256个中断,其中包含了16个内核中断和240个外部中断,并且具有256级的可编程中断设置。但STM32并没有使用Cortex-M3内核的全部东西,而是只用了它的一部分。STM32有84个中断,包括16个内核中断和68个可屏蔽中断,具有16级可编程的中断优先级。而我们常用的就是这68个可屏蔽中断,但是STM32的68个可屏蔽中断,在STM32F103ZET6中只有60个。: N* m5 t7 c: G7 u' E) t 9 P+ q! U" }5 P9 v& ~' ?9 {; x 3.2 STM32F103中断优先级0 o) K$ y6 E9 n; U# x 3.2.1 优先级结构, m8 C( i% D- Y# k7 ~8 I% e( t STM32F103的中断分为抢占优先级和响应优先级两种,这两种优先级的顺序是抢占优先级高于响应优先级,假设存在两个事件,那就会存在以下几种可能:& k$ @' k) t' k' @ 7 W4 S# x' a0 m: Y6 K (1)情况1:事件1和事件2的抢占优先级都是1,事件1的响应优先级为1,事件2的响应优先级为2,那么事件1和事件2同时发生的时候,CPU优先处理事件1,然后处理事件2;/ O2 {$ y6 _" [, r4 K- y: j. I ) x$ x) F6 U! ~6 E/ f' B (2)情况2:事件1和事件2的响应优先级都是1,事件1的抢占优先级为2,事件2的抢占优先级为1,那么,事件1和事件2同时发生的时候,CPU优先处理事件2,然后处理事件1;" Y) y9 `' g" T0 L: J& V" M* w X4 K+ k4 q# r' Z8 O& l (3)情况3:事件1的响应优先级为1,事件2的响应优先级为2,事件1的抢占优先级为2,事件2的抢占优先级为1,当事件1和事件2同时发生的时候,CPU优先处理事件2,然后处理事件1; # a1 Y( A6 J( h1 j 通过上面两种情况,我们可以发现,当抢占优先级一致,谁的响应优先级的数小,谁的优先级就高,中断同时发生的时候CPU就先处理谁;如果抢占优先级不一样,那么无所谓响应优先级,谁的抢占优先级数小,优先级就高,中断同时发生的时候CPU就先处理谁。 7 j! r: E' g! N' ?2 @$ { STM32F103的抢占优先级和响应优先级各有4级,即0~3,根据乘法原理,也从侧面反映了16级可编程的中断优先级,并且抢占优先级和响应优先级的数量是可以设置的,通过中断分组来配置,中断分组和优先级数量的对应如下表所示。, G+ y& o/ ^7 L" u5 `# M

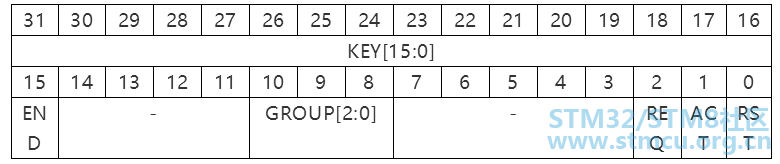

3.2.2 相关寄存器; g+ {. q G9 V, a0 C% L (1)中断应用和复位控制寄存器:AIRCR

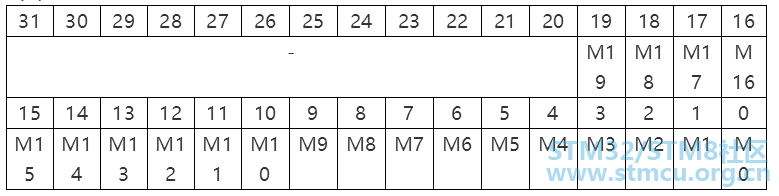

Bit 31~Bit 16:激活代码,写入0x05FA激活寄存器 Bit 15:指示数据的字节序(这只能在重置后更改)( P6 W- u8 w3 U' T( A- f+ y$ w . w( d% ]0 X% n0 I" `! L9 ` 0:表示小尾数 2 o1 ?# O9 z `9 P) t4 _ 1:表示大字节序& Q0 h' @- n* v# M Bit 10~Bit 8:中断优先级分组 Bit 2:请求芯片控制逻辑产生复位 Bit 1:清除所有活动状态信息中的异常 Bit 0:重置Cortex-M3处理器(调试逻辑除外)! i( Z3 |: `8 R; k$ S0 S+ p/ {( t (2)中断使能寄存器组:ISER" p( E: }7 m( [ a4 Z 2 C z% e. J' b 在STM32中,ISER寄存器一共有3个,ISER[0]的0到31位对应中断0~31,ISER[1]的0到31位对应中断32~63,ISER[2]的0到3对应中断64~67,如果需要使能某个中断,必须设置对应的ISER位为1,要清除的话可以设置ICER寄存器组对应位为1,或者对ISER写0,但是对于ICER寄存器组写0是不起作用的。 - X/ @* `/ ]' n) N (3)中断优先级控制寄存器组:IP) y$ v( e, t/ p: h

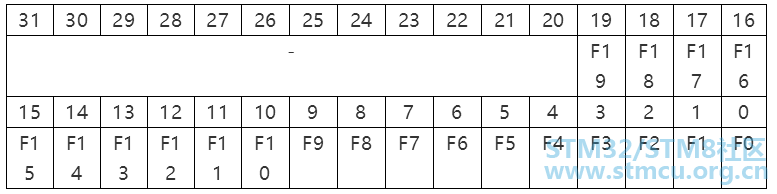

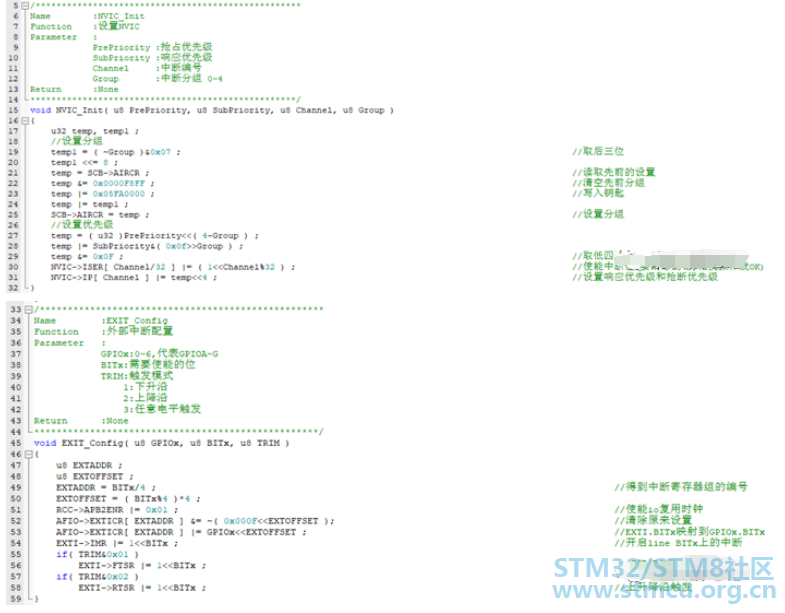

对于STM32,优先级控制寄存器IP一共有68个,对应着68个中断,每个寄存器的结构都是相同的,如下图所示。5 c" q$ x+ e Z9 k2 q0 _- E" w. P / i4 M' H6 D/ A- \. F1 z( [ 9 B0 ~0 e& u$ J, g. x1 i Bit 7~Bit 6:抢占优先级0 p; |) d2 B: u; U- t Bit 5~Bit 4:响应优先级' H, b2 f/ i' I6 h 3.2.3 中断优先级配置函数! a* R) O8 f7 z W

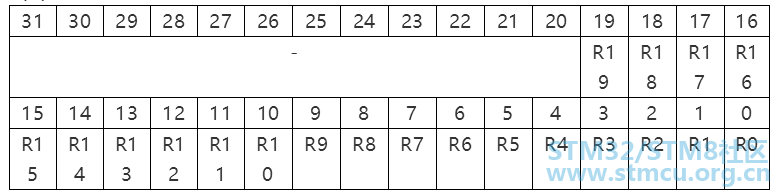

3.3 外部中断EXIT结构 3.3.1 EXIT概述 S" p% e: v- x* [! W 外部中断/事件控制器由连接线设备中的多达20个边缘检测器或其他设备中的19个边缘检测器组成,用于生成事件/中断请求。每条输入线可以独立配置以选择类型(事件或中断)和相应的触发事件(上升或下降或两者)。每条线也可以独立屏蔽。; t7 z9 x }- G; k, `5 { 对于STM32来说,每一个端口都可以配置为外部中断,根据中断信号的类型都可以单独配置上升沿触发或者下降沿触发,中断服务函数相互独立。8 z$ j" H; y: S6 @ ' P7 ]3 R" d1 c) i8 o- i; S# K+ p 3.3.2 EXIT相关寄存器 (1)中断屏蔽寄存器:IMR

it 19~Bit 0:线x上的中断请求配置位 0:禁止输入线x上的中断请求" `; H5 I% ?. a" m$ T 1:允许输入线x上的中断请求 5 d1 x' v+ D# E: b \ (2)上升沿触发选择寄存器:RTSR

it 19~Bit 0:线x上的上升沿触发事件配置位 ) s7 g: C1 q# j6 v 0:禁止输入线x上的上升沿触发 1:允许输入线x上的上升沿触发& l2 ^! }; c2 J, J0 j: h 0 D O, P6 ]6 Q9 a" f8 L1 O (3)下降沿触发选择寄存器:FTSR1 W' A! k. h- w* l9 @+ C7 H. h ; G9 x( M6 L8 `: n. }3 @6 Z

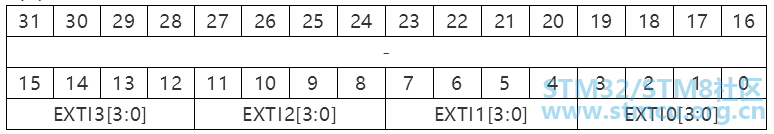

Bit 19~Bit 0:线x上的下降沿触发事件配置位 0:禁止输入线x上的下降沿触发3 r/ ^. }6 W7 ~: D 1:允许输入线x上的下降沿触发- ]" ^6 ~' c! l5 u, |& r (4)外部中断配置寄存器1:EXTIXR1 + T. o1 B3 {$ L' i1 B* p U3 b

EXTIx[3:0]:EXTIx配置(x = 0~3)- Y$ j# L* h' ]* S/ G2 _& t& Z , X5 e- n' L' p9 J/ z 0000:PA[x]引脚 0100:PE[x]引脚 0001:PB[x]引脚 0101:PF[x]引脚+ e" ~. k- v" q 0010:PC[x]引脚 0110:PG[x]引脚 0011:PD[x]引脚 (5)外部中断配置寄存器2:EXTIXR2

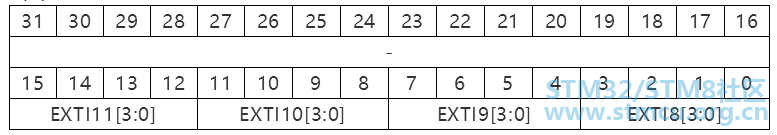

EXTIx[3:0]:EXTIx配置(x = 4~7) 0000:PA[x]引脚2 U5 F* ?8 {; ?# s, e8 u 0100:PE[x]引脚 0001:PB[x]引脚8 a' |. \' D) b9 Y1 V+ x' ? 0101:PF[x]引脚 0010:PC[x]引脚 0110:PG[x]引脚 0011:PD[x]引脚3 m! W8 T& m, w 5 N! ^7 p2 Y8 @# C5 c (6)外部中断配置寄存器3:EXTIXR3: [3 f; U: e, e& v! s : W4 F7 Z# ? m( H

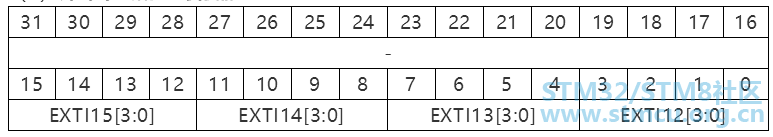

EXTIx[3:0]:EXTIx配置(x = 8~11) 0000:PA[x]引脚 0100:PE[x]引脚 0001:PB[x]引脚" A- k1 s, e! i1 B- G7 r; ^3 u8 E4 K 0101:PF[x]引脚 0010:PC[x]引脚 0110:PG[x]引脚( E' b* q7 k/ c' y 0011:PD[x]引脚3 x' o" G: r1 S# f w : O- v$ @7 l" } (7)外部中断配置寄存器4:EXTIXR43 _6 F$ p8 L2 |1 q& Y R O& Q/ | \ L2 g EXTIx[3:0]:EXTIx配置(x = 12~15)- S5 c" z# x, B5 |2 F4 |' @- {8 m

0000:PA[x]引脚 0100:PE[x]引脚: d# y7 R$ h# h4 @ 0001:PB[x]引脚 0101:PF[x]引脚 0010:PC[x]引脚 0110:PG[x]引脚2 j; S9 \+ j/ h& _! G- T5 R 0011:PD[x]引脚, v! r( \; ^* s: N$ g& O- u: a" u $ a% i0 Z {1 z4 L$ T (8)APB2外设时钟使能寄存器:APB2ENR 8 m3 B! m s6 o; z5 F+ B# o$ i

Bit 14:USART1时钟使能(写1开启,写0关闭) Bit 12:SPI1时钟使能(写1开启,写0关闭); P' c" S% Z8 L6 V5 f1 ]# h6 L/ M0 B Bit 11:TIM1时钟使能(写1开启,写0关闭)( P. M9 [0 Q8 _: c# Z+ }* @ Bit 10:ADC2时钟使能(写1开启,写0关闭)6 s* D1 `( o6 X$ T. p; e& } Bit 9:ADC1时钟使能(写1开启,写0关闭)- Y. I2 R7 X% D% Y& m) [% w Bit 6:GPIOE时钟使能(写1开启,写0关闭); E- n; x: Q5 Y9 n. q+ w Bit 5:GPIOD时钟使能(写1开启,写0关闭) Bit 4:GPIOC时钟使能(写1开启,写0关闭) Bit 3:GPIOB时钟使能(写1开启,写0关闭)1 L, v' O- U; X) k% B# E7 p- q5 G; z Bit 2:GPIOA时钟使能(写1开启,写0关闭)& Q# a% G, U) m! y. u9 X+ [ Bit 0:辅助功能IO时钟使能(写1开启,写0关闭)/ v0 `1 y" z& ^8 P ; [' r/ l* b' h9 v 3.3.3 外部中断配置函数 ; N+ h' S' `3 E. K( N

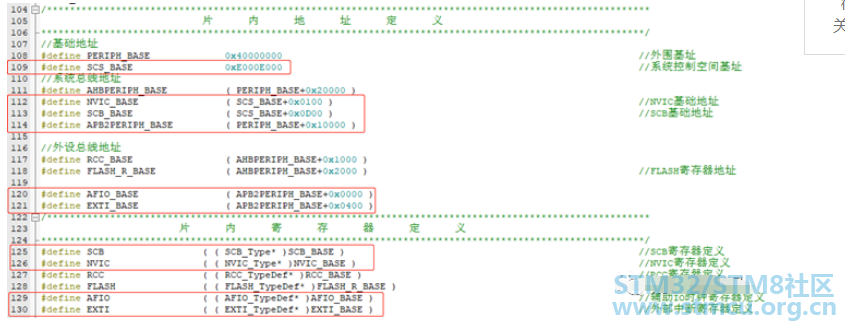

- ?; L$ j' A0 }# ]3 ] 3.4 其他文件的添加 3.4.1 寄存器定义文件 (1)添加用到的NVIC寄存器组和EXTI寄存器组的定义。/ k& C" O8 Y0 ?

(2)定义寄存器组地址

3.4.2 sys.h文件

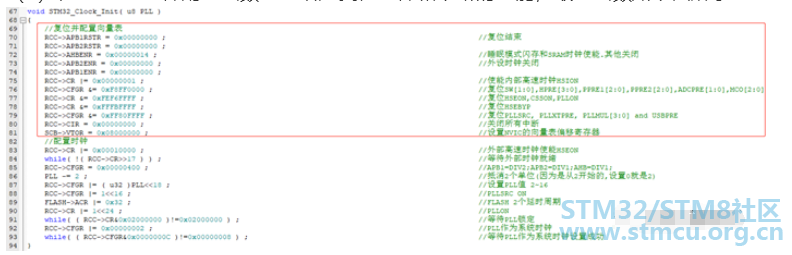

上图就是添加子函数声明,为了用于其他文件调用。* F( V4 `+ ?! ~5 A# B1 E# ~ & } i0 V: J4 }/ ?1 Q8 t) T 3.4.3 sys.c文件 (1)在STM32时钟配置函数之前增加复位时钟和中断的功能,最终函数如下图所示。

(2)添加刚才的两个子函数

至此,sys文件里面最基础的函数就全部添加完毕了。9 v) Z1 i; @/ g& M# z: D9 K- Z ( q2 N3 ?0 B: V$ L! m . x2 t* d! F" d2 X9 [5 B 上一篇: STM32学习笔记02—时钟树架构 $ R, t# ]% r& F; R% n |

|