编写基础RCC(Reset and Clock Control)

5 D1 c0 N% s+ m( U' k K3 n, j" x

8 \! e7 @" O6 l5 @% A% |1 v, P. g/ v1 y( Y6 E8 q

# w, F a) ~% l! SAHB、APB1、APB2最大频率都是170MHz。

2 M. _7 G+ a- s& Y

! Z- E2 g5 ]7 ?

2 D3 k3 B- i! s% @7 X; D; k9 @7 i2 N# @/ o* N3 z! |

! K2 q1 D" u! }+ P3 o+ w- X/ Q

! e7 U( V2 }# o时钟树# h0 b. Y" R- A o* n0 [

+ i& r$ V# F/ h( g. G要想配置时钟首先必须要看明白时钟树。

$ o: f, }/ g- \8 o) N" `8 Y

5 `# X: X5 K( d* v& m; F/ {0 f* ^1 o

: ^7 I' r5 N* qPLL9 q; P% O3 R# r: p. F+ b6 v$ k

* q; `5 k3 k4 P3 R2 b1 X

配置时钟精髓就是PLL倍频,因此搞清楚了它就很好解决了。

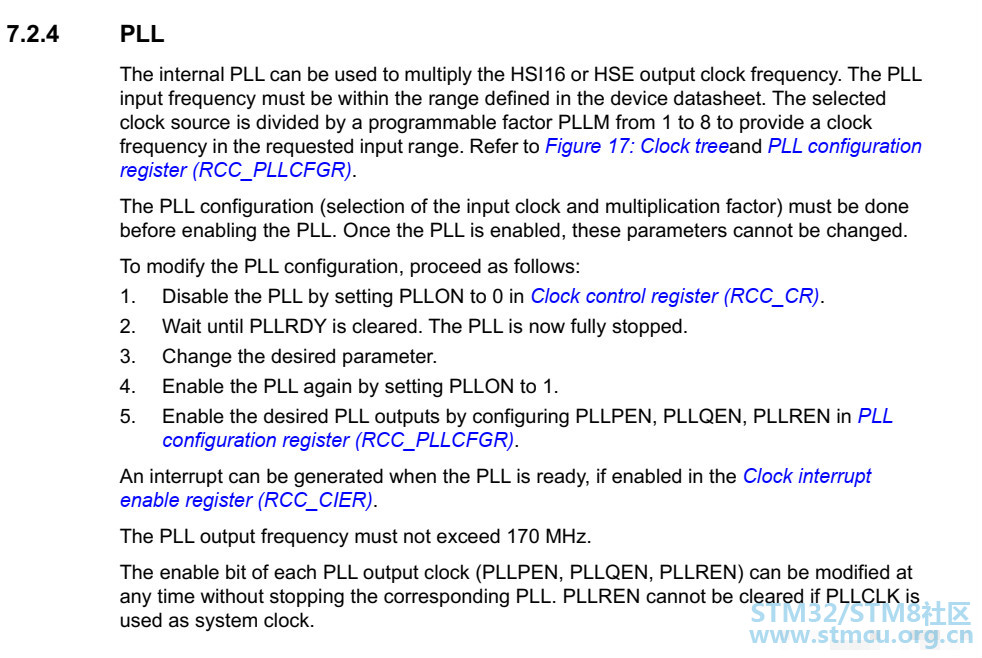

$ _( u7 h! r5 F# { y" [; `& z8 k手册上对PLL配置步骤如下图:

- z+ D, {% ^ E2 Q7 X8 V' f

0 t' X5 k. m \$ P7 L

首先通过上面的时钟树也可以看出来PLL的时钟源有两种:HSI、HSE。PLL的分频、倍频配置在RCC_PLLCFGR寄存器中。

; p1 h% x- P" k配置PLL的过程是:

6 l. e) C' K& f, I7 @# l1 y4 w2 m+ X

5 C* ]% Q8 p2 c- 将RCC_CR的PLLON位清零来关闭PLL。

- 查询RCC_CR的PLLRDY是否被清零了,如果该位为0说明PLL已经关闭。

- 配置分频、倍频系数等(单纯的使能或者关闭PLL_P、PLL_Q或者PLL_R不需要这些步骤,直接操作即可)。

- 将PLLON设置为1,再次启用PLL。

- 通过在RCC_PLLCFGR寄存器中配置PLLPEN、PLLQEN、PLLREN来启用所需的PLL输出。 注:PLL输出频率不得大于170MHz。 当一个时钟源被直接使用或通过PLL作为一个系统时钟,是不可能停止它。1 V2 i0 \. i3 p. s5 _3 b

R, ^# V. v* c9 z" W. X

8 m! d5 T/ k5 j+ W' K

5 w. o8 m" S; x: T) S9 Z

PWR

- a X" g' E% v' P/ o+ P3 F# R) B# l c! J; V

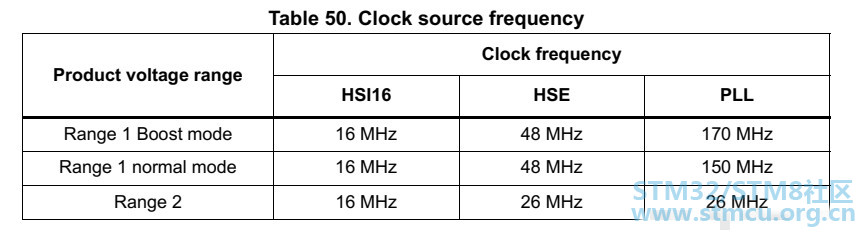

在不同的工作频率下,对应的电源模式也不一样。

- g1 N; T0 T. ~, q* M可能是为了满足不同频率下的功耗管理,高时钟对应高内核电压,我使用TI的5529时也有倍频时修改内核电压的的操作。. B5 d7 `3 d& i" w

g474的电源模式与各个时钟频率对应关系如下表:

5 {4 P0 `/ p6 O, p/ }/ k

' Y" X+ \. j6 u7 t& H

2 O4 f# o' j5 {, o$ q/ s) X' P

% m/ a5 H) v j* ~

PWR_CR1的VOS[1:0]对应Range2和Range1:' o6 q5 u3 o. o. y

$ r( r2 R) ^! h7 l6 U+ Y8 s

5 f/ H' J Y: M% b& G0 m R

4 }6 y2 z z+ N: K- m, Q

$ g2 `# d ^' v$ v+ I

至于Range1的normal模式和boost模式是在PWR_CR5寄存器的R1MODE位配置,R1MODE为0就是boost模式:

! q; p, e0 `" h5 ]2 V- K1 s; s- g" F) ^! F

) H) T6 l: s8 \& ^

1 u( }. i! F+ O+ r3 x

/ ^3 ]% m2 z$ A( C

g474的R1MODE位与SYSCLK的对应关系如下:

# `9 S8 s% `2 Q& t( o A) B

9 M5 A+ B& m4 C p9 v+ u4 g1 H

: i0 |2 b6 f$ M9 U2 F% D

, X$ H% M k8 A) w" E* g

6 ]$ A4 z5 ~( U手册中还介绍了从range_normal切换到range_boost模式的步骤:

2 E, Q( R: p: ]6 q* r& M

: [( X. \# \) s3 s! m, d, I# l

2 g' n; a0 l! J- I$ s7 t. Y- S/ U

! a5 I& s. H; _. r$ M# K

6 e# p! n# v8 M) n8 N

; i# L9 _2 J: O- d$ o7 s

- 在切换到更高的系统频率之前,系统时钟必须用AHB分频器除以2。

- 清除的R1MODE位在PWR_CR5寄存器中。

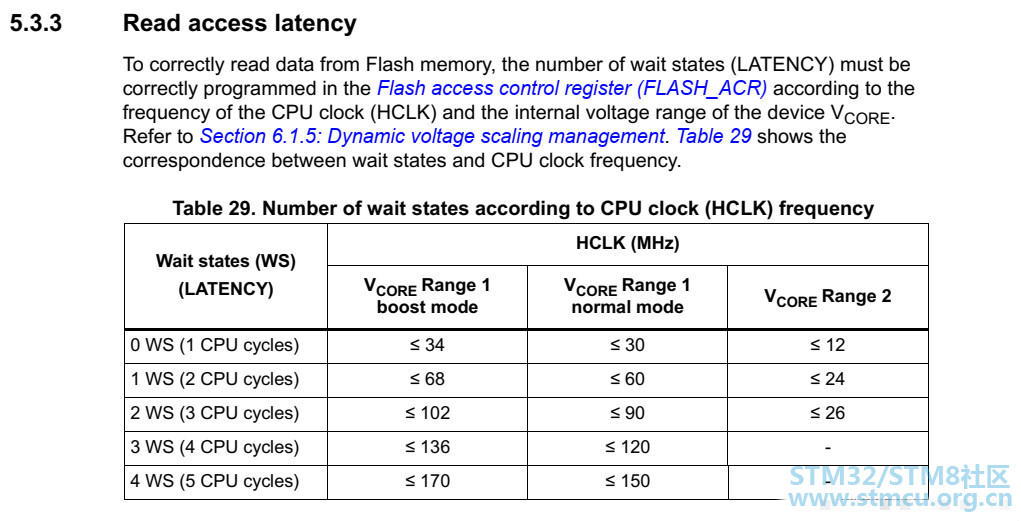

- 在range1 boost模式中,根据新的频率目标调整等待状态的数量。

- 配置并切换到新的系统频率。

- 等待至少1us,然后重新配置AHB预压器以获得所需的HCLK时钟频率

% [0 M3 C' S. O( ?; j" B& a h3 F* j. [/ I0 }

7 ?: o" U( T6 N

" v3 T! C6 y+ }% g% ^1 i7 ]- ~

FLASH

$ v$ \; g# h7 k" l2 b! }! S9 Q+ B7 B

这个是我原来忽略的地方,原来就配置了PLL和PWR,然后倍频到140MHz就是极限了,后来我反复查阅手册,才发现了原来少了对FLASH的访问比率的配置。(可以看到上面的range_normal切换到range_boost模式步骤里已经提到了修改FLASH访问比率的事,但是由于没看懂是什么意思,还以为是延时1us,因此配置170MHz时候就失败了。) ) N, j3 ~1 I/ Y$ |! |' ?% X. H

上面提到range_normal切换到range_boost步骤里有这么一句:

3 d4 _ L' K7 r( B5 G

- 在range1 boost模式中,根据新的频率目标调整等待状态的数量(FLASH_ACR的LATENCY位)。9 k* y& Z5 F- i* O0 T

& ]) l& ` | @' ]5 @# `9 }) ?

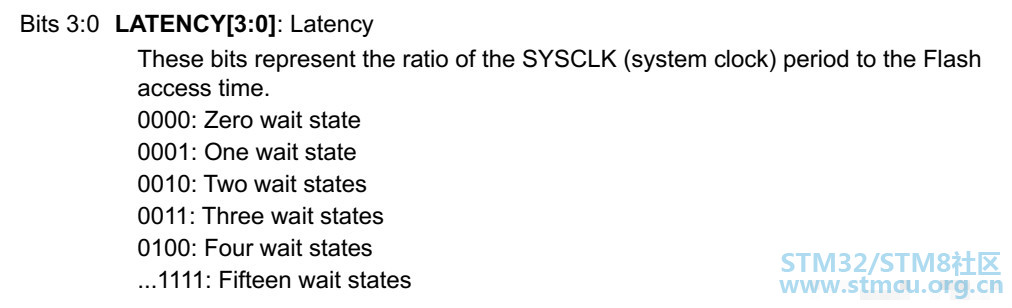

那么就看看这个 FLASH_ACR 的 LATENCY到底是个什么。

$ z: k7 k1 B9 z3 i% f" ~+ S查阅手册找到这个寄存器:

- U7 C/ ?2 c$ [5 A

+ ~% z0 W5 N0 V( }7 G' p! Z; _9 _( J. ]/ {+ C x: H

7 r& f, c+ e/ z; Q6 q可以看到LATENCY在最低位:% h `' E7 S+ G' b

4 v Z: a7 U, h3 J

" j0 S" q2 O4 {! O* B, G# |

0 a* G9 v$ A: R! @0 \

, i' n: I; Z. k2 B+ x

+ z6 d- L* T& A& {+ ~LATENCY[3:0]:这些位表示SYSCLK(系统时钟)周期与Flash访问时间的比率。

$ \' t5 T+ f7 s% h" N# F2 w知道了它是干嘛的,那么它到底设置为多少合适呢?如下图所示:

, P; S+ `# _9 y0 [) ~/ ^

: h! A' o( @- q

+ o2 Y+ i. T$ |; v h

* D4 f, j6 D- ~/ C1 ~) M3 L9 N为了正确地从闪存读取数据,等待状态(延迟)的数量必须根据CPU时钟(HCLK)的频率和内部电压范围的设备VCORE被正确地编程在闪存访问控制寄存器(FLASH_ACR)。参考第6.1.5节:动态电压缩放管理。表29显示了等待状态和CPU时钟频率之间的对应关系。$ n/ f9 @# h; d! p! t0 Z+ x

$ m; m: b* U* y8 J$ A

对号入座,我要设置为170MHz,模式为Range 1 Boost模式,那么对应LATENCY值应该为4WS,因此将其配置为4。

/ Y* ?* U1 E( X% c5 A( J

FLASH->ACR |= FLASH_ACR_LATENCY_4WS; 0 A5 ]% C1 [7 q# o/ e* m( L4 F

配置函数

5 n0 j: B" {$ u$ }" M

5 W* ?5 h Y/ V有了上面的概念就可以进行编写时钟函数了。3 R& z" O I$ E/ J

步骤如下: $ x* p( }9 e! U0 b7 S0 X

- 开启HSE(鄙人的板子HSE为8MHz)并确认HSE就绪;

- 关闭PLL并确认PLL已经关闭;

- AHB二分频;

- 配置为range1_boost(默认复位为range1_normal模式);

- 配置FLASH_ACR的访问时间比率;

- 配置PLL;

- 打开PLL并确认PLL就绪;

- 使能PLL_R;

- 配置系统时钟为PLL输入,并确认系统时钟就绪;

- 延时至少1us后切换AHB为不分频。8 u( J6 H' V$ E5 F

7 v# U5 w; I \) q% E" r

' I& p7 N z3 V" [& b# y, |- u8 SYSCLK_140MHz(void)

0 q0 b- s7 a8 K% X E: w* i4 { - {( o7 {. K5 r8 l8 J

- u16 temp = 0x2000; J3 X2 n3 N1 J# H' |& E( R. s

- RCC->CR |= RCC_CR_HSEON;//打开HSE

( ?- T! i$ U" O% K, d - while((!(RCC->CR & RCC_CR_HSERDY))&&(--temp));//等待HSE就绪

3 H4 x$ D! D- N; ^0 V- R# o* l& c - if(!temp)//检查是否超时: n+ g6 ~6 Y5 |; B

- {

- G$ N6 R& q; A0 O" F% P e | - return FAILED;- H% Z+ V$ A; N

- }$ k2 q4 H* |/ m

- RCC->CR &= ~RCC_CR_PLLON;//关闭PLL9 a- d' M0 a% f

- temp = 0x2000;

+ b( Q" R! d0 |3 ]% ^0 q- m2 E/ |- V( r - while((RCC->CR & RCC_CR_PLLRDY) && (--temp));//等待PLL下线

3 j* t! \% O5 ]3 \/ ~8 D4 ~ - if(!temp)//检查是否超时7 c4 {5 w; l: c

- {

! t0 Q3 `4 \& p7 G - return FAILED;

' \; m, c( [! W4 T' S+ v' i5 s - }

# S% ^2 s# ]! c$ d& l- v7 S - RCC->CFGR = RCC_CFGR_PPRE2_DIV2|RCC_CFGR_PPRE1_DIV4|RCC_CFGR_HPRE_DIV2|RCC_CFGR_SW_HSI;5 C7 r' f7 j; p

- //系统时钟选择内部高速时钟,AHB二分频,APB1四分频,APB2二分频

: g8 H# a6 d) L% f' \ - temp = 0x2000;( ]: r# i7 J8 r/ A/ q0 u, L: _

- while(--temp);//等待AHB稳定$ F+ \% B) B5 T9 T& j

- PWR->CR5 &= ~PWR_CR5_R1MODE;//设置为range1_boost模式

) c. E t* r, J/ c0 t, C, q+ D: X% I - FLASH->ACR &= ~FLASH_ACR_LATENCY;//清除LATENCY; {4 e" j* K& _% K9 D! g4 B* ^

- FLASH->ACR |= FLASH_ACR_LATENCY_4WS;//配置LATENCY为4WS

1 U2 D0 B6 s- L - temp = 0x2000;

; R e- r! |$ q6 u" x - while(--temp);//等待系统稳定7 ?/ Y7 m% Z2 Q; g% W1 ~

- RCC->PLLCFGR = (70<<RCC_PLLCFGR_PLLN_Pos)|(1<<RCC_PLLCFGR_PLLM_Pos)|RCC_PLLCFGR_PLLSRC_HSE;//(8*70)/2 = VCO = 280MHz7 A, V N+ I8 m9 }6 ?! @; Q+ D

- RCC->CR |= RCC_CR_PLLON;//打开PLL& y/ Z, R' g$ l% ]7 A

- temp = 0xf000;

& c" _' H/ L1 X5 ~+ N$ j3 o9 v- M - while((!(RCC->CR & RCC_CR_PLLRDY)) && (--temp));//等待PLL准备就绪/ j8 d! v: c [' `. {

- if(!temp)7 m5 l( n8 X' h* u% j

- {/ D5 U& x; I; J, P& Z

- return FAILED;

: G$ [5 ?; v+ F - }

/ B1 r0 `. ^$ v0 S, x. V# p, | - RCC->PLLCFGR |= RCC_PLLCFGR_PLLREN;//使能PLL_R

; o8 f0 [+ P; o- ~7 l( O - RCC->CFGR |= RCC_CFGR_SW_PLL;//设置系统时钟选择PLL5 U6 H, `: U! s9 T7 @) C

- temp = 0xf000;" s: Y) n+ l: f$ }2 w* m, \

- while(((RCC->CFGR & RCC_CFGR_SWS) != RCC_CFGR_SWS) && (--temp));//等待系统设置PLL主时钟完成标志位置位1 E# n: D8 n; i4 V V

- if(temp)

) ~' s4 b6 Y/ L; @ D$ {9 x - {

/ ~# ]1 J7 X j0 a; d5 B. G - temp = 0;9 k: m" i/ A: b5 @: {& e( ~+ v2 q

- while(--temp);//等待系统稳定5 i) S8 `0 B$ O$ J, \) Q* O; k3 p

- RCC->CFGR &= ~RCC_CFGR_HPRE;//AHB 不分频 == SYSCLK2 m, K1 m5 D+ {' l; ~: E

- return SUCCEED;+ j e5 C8 O+ }4 ]& ]2 r' e

- }

1 P7 s# p7 Z0 ?7 i, f, w+ f - else" f' |; d( y! h9 x1 s

- {/ C) }' x+ E9 a( s

- return FAILED;

4 q( k, [* M3 `# T) w - }

+ x0 n0 m& c1 q - }

. b. a8 S' _) f

% J* K% k/ e w$ T5 x

然后就配置结束了,通过定时器验证确实为170MHz。

% r$ b$ G) O5 E0 @% ]

( R/ r3 t4 G, a+ z' w% O9 N

附录:RCC寄存器6 h: U3 I6 J$ j0 S" F* N0 }

1 S8 q. P& p/ |9 t9 y. ]& d

最后:

7 m5 n+ Q6 X. [6 |% J附上本人写的寄存器配置,方便个人配置,要啥直接删注释就好:

2 I2 F1 B* P( H( X! q) t y7 W

- //================================RCC->CR========================================, b' x/ T* \3 F: l# U# V3 y

- RCC->CR |= 0 //default: 0x0000 0063

/ e2 K0 x$ M5 ~+ Y$ O" H+ F - // //RCC_CR_PLLRDY //bit25【read only】: PLL Ready

/ r+ Y: f8 @) x9 V. s+ V - // |RCC_CR_PLLON //bit24: 使能PLL。

. S4 h3 `* i7 Z6 I8 \9 t, ] - // |RCC_CR_CSSON //bit19: 时钟安全系统使能。0 OFF ; 1 ON

$ J7 V7 `+ h. o0 X' z, M - // |RCC_CR_HSEBYP //bit18: 0 HSE晶振不旁路 1 HSE晶振旁路* d) a8 `. v$ X- B

- // //RCC_CR_HSERDY //bit17【read only】: HSE Ready

1 @' l9 G3 j' [" u- y - |RCC_CR_HSEON //bit16: 使能HSE

/ P. u8 v# Z2 D2 V/ p* k8 w - // |RCC_CR_HSIRDY //bit10: HSI16时钟准备就绪

& e4 }. l5 Y% m- V7 |6 O - // |RCC_CR_HSIKERON //bit09: 停止模式HSI是否启动! r7 \4 P9 N( E' {

- // |RCC_CR_HSION //bit08: 1 HSION 0 OFF5 R: _6 j& W3 U- e0 O5 O- M O

- ;

$ g r9 j0 H) C9 R a+ z

/ t; Z/ i! X5 P( b7 m" n- //================================RCC->PLLCFGR ========================================

% y, n& W" l% h1 q8 [ N$ D - RCC->PLLCFGR = 0 //default: 0x0000 1000/ S/ V& [* D; g

- // |RCC_PLLCFGR_PLLPDIV //bit31-27[4:0]: P 分频 给ADC用$ d; c" J6 ?7 z! t7 j- K# d7 E

- // 00000: PLL “P” clock is controlled by the bit PLLP

) T, Z2 |- o/ }' d - // 00001: Reserved.8 a7 Z& P7 g. }! p# K/ Q

- // 00010: PLL “P” clock = VCO / 2

' }, |, E _, f6 H - // ....% J5 E( i0 g' H) i! Q6 z

- // 11111: PLL “P” clock = VCO / 31

1 E+ e+ j# q/ d- R8 w, }& c - // |RCC_PLLCFGR_PLLR //bit26-25[1:0]: 锁相环R 分频! [5 J w$ d/ m& ^, C

- /// // 00: PLLR = 2* x. ^( Q) I3 s

- // 01: PLLR = 4

7 G# d1 s! B( v' O! o, r/ o - // 10: PLLR = 61 G- ]! K/ {+ l, K1 h

- // 11: PLLR = 8" {' q3 Z& |3 F4 ^6 Z

- // |RCC_PLLCFGR_PLLREN //bit24: PLLR使能1 y" @0 R z' E" c" S- G

- // |RCC_PLLCFGR_PLLQ_0 //bit22-21[1:0]: Q分频,USB用。分频参数与R分频一样4 I7 I2 C. Q# h3 a( k

- // |RCC_PLLCFGR_PLLQEN //bit20: PLLQ使能

9 z' a( K3 @) z - // |RCC_PLLCFGR_PLLP //bit17: P 分频

$ Q7 b2 c# V+ `9 \3 w3 @) Q, \ - // 0: PLLP = 7* y6 [ P$ T/ L+ ?

- // 1: PLLP = 17

, |, O& v7 l! V* I+ E) t - // |RCC_PLLCFGR_PLLPEN //bit16: PLLP 使能6 H2 t- y0 i9 s ]" J; O

- //----------------------- VCO = 280MHz- [; a+ Y5 y& U$ K5 s5 `% T

- |(70<<RCC_PLLCFGR_PLLN_Pos)//bit14-08[6:0]: PLL的倍频 不能小于8

- t2 X9 a( p& J# a" O5 L0 B4 h - // 0000000: PLLN = 0 wrong configuration

% m' u% Z$ C. l5 W/ V6 z* Z - // 0000001: PLLN = 1 wrong configuration

: I2 ]5 @5 ^2 g: A3 J# r! m( w - // ..., X2 i. s) x w3 N0 u1 u, `4 M: D

- // 0000111: PLLN = 7 wrong configuration4 j1 t$ F) g& v [- H

- // 0001000: PLLN = 80 q' a0 O5 Y; t, `

- // 0001001: PLLN = 9# k! a( R9 Z4 ~1 l

- // ...

6 _% c( \0 s& A) Q/ E# @" P - // 1111111: PLLN = 127

7 G1 v5 I% V& { - |(1<<RCC_PLLCFGR_PLLM_Pos)//bit07-04[3:0]: PLL初始分频1 i5 P, x ~( f; _8 `

- // 0000: PLLM = 1# P) x$ n' h; i, i) l

- /// // 0001: PLLM = 2% l8 x7 M' S3 l9 T* U- O+ r$ `

- // 0010: PLLM = 35 }8 q- c" c, z3 P" c

- // 0011: PLLM = 4

4 Y8 U: e9 ^: y) \ - // 0100: PLLM = 5

) r' ~2 D6 w0 D - // 0101: PLLM = 6

/ n3 ]3 q, n: g$ a* i: W - // 0110: PLLM = 74 _0 [# v6 c `1 p0 g' c; R0 x H

- // 0111: PLLM = 85 u }& r! [6 A8 M

- // 1000: PLLSYSM = 9

$ f8 b- c$ k. ^$ \" C# K. c - // ...8 I9 b3 c* a. G; p( p, M

- // 1111: PLLSYSM= 165 D5 Z$ `$ C% }) [) `

- |RCC_PLLCFGR_PLLSRC //bit01-00[1:0]: PLL时钟源选择。

* x. n8 C& u1 U# u R. w - // 00: No clock sent to PLL' l6 k5 H) x/ E3 r' M( ]5 d) ]

- // 01: No clock sent to PLL

( X3 ?$ ]5 S+ \! D% z5 V - // 10: HSI16 clock selected as PLL clock entry

0 Y$ P% {' }4 V0 T( k - /// // 11: HSE clock selected as PLL clock entry

( y# H. U4 [7 G* r' B; h; O2 ~ - ;

$ O7 F8 q. z/ `% A7 _& b: e. n1 f# G

) A2 L" Z. J; H6 p- //================================RCC->CFGR========================================

: |2 I, [$ j' T8 N+ M! O - RCC->CFGR = 0 //default: 0x0000 0005% K; U7 ^: m; h$ M: V4 ?+ Z- j' r

- // |RCC_CFGR_MCOPRE //bit30-28[2:0]: MCO输出时钟分频6 ^ t' g, B- F( } B2 h1 W- K

- // 000: MCO is divided by 1

4 u" s- E0 s" p+ {; p9 n - // 001: MCO is divided by 2- ]* V! \* l8 r' I& l/ O1 ~

- // 010: MCO is divided by 4. L5 R6 f( o" Q4 [7 {, w

- // 011: MCO is divided by 8

3 U$ R$ f# K8 {& M$ S+ y - // 100: MCO is divided by 16

l. R& v6 J4 F- C D) M - // Others: not allowed. K) P% C/ \9 q; p1 u

- // |RCC_CFGR_MCOSEL //bit27-24[3:0]: MCO输出时钟选择2 H" u+ g& p5 m# v, W7 v

- // 0000: MCO output disabled, no clock on MCO' ^! `9 B5 f+ t; d7 p5 W- Y

- // 0001: SYSCLK system clock selected. E# Z& U; Z7 p* ]

- // 0010: Reserved, must be kept at reset value6 o& X+ S0 K \' V" s* i

- // 0011: HSI16 clock selected$ l4 u8 E! r- p+ ^

- // 0100: HSE clock selected3 t, v' \, l- F/ n. k

- // 0101: Main PLL clock selected

8 Q1 ? m R8 r) G: S4 q! ^+ I - // 0110: LSI clock selected9 |. C1 W7 H* w8 S+ v( ?! Q

- // 0111: LSE clock selected! a- N# D8 j6 w' I: u4 O( r

- // 1000: Internal HSI48 clock selected

5 T8 k! }- H; y2 m6 P3 Q, | - |RCC_CFGR_PPRE2_DIV2 //bit13-11[2:0]: APB2预分频/ T4 h }' c! D9 Q# D' O, U

- // 0xx: HCLK not divided9 `6 \; c# a. F8 H

- // 100: HCLK divided by 2

( M2 m* d& G8 Y7 Q9 H$ u, J) _ - // 101: HCLK divided by 4

8 z) J4 i1 ]% [ - // 110: HCLK divided by 8

) m1 I7 T+ v* j1 a$ P# ^ - // 111: HCLK divided by 16& S5 Y0 n% w5 F; @

- |RCC_CFGR_PPRE1_DIV4 //bit10-08[2:0]: APB1预分频

& b8 t$ g3 n W - // 0xx: HCLK not divided

* S9 Q/ H2 m' \4 f; A2 C - // 100: HCLK divided by 2

T) I# k* s% N9 ? - // 101: HCLK divided by 4

& b( j; w2 Z. H- M% p _1 R - // 110: HCLK divided by 8

& N* H: Q0 y8 {+ R6 K- A - // 111: HCLK divided by 16* f0 r% G( E X5 W

- // |RCC_CFGR_HPRE //bit07-04[3:0]: AHB预分频(改变core电压之前应该先查看这些时钟频率)' I; v: W" N/ }

- // 0xxx: SYSCLK not divided

& {! C3 K+ u S - // 1000: SYSCLK divided by 2- |/ }4 a( ?6 \! O

- // 1001: SYSCLK divided by 4

6 m! I: ]! X1 |: e. ~ - // 1010: SYSCLK divided by 8

R6 ]1 H6 G- L: p - // 1011: SYSCLK divided by 16

' u+ f( ^& r! ^7 O+ \% B+ v - // 1100: SYSCLK divided by 64

0 ~0 h r% a% J) y! V5 F - // 1101: SYSCLK divided by 128/ z* C6 R6 B, {$ A

- // 1110: SYSCLK divided by 256

, W0 m( a/ t9 ]& S6 h: @3 I - // 1111: SYSCLK divided by 5127 n c3 b: x8 ^3 ~

- //RCC_CFGR_SWS //bit03-02[1:0]【read only】:系统时钟源选择状态,该位与SW对应。! A8 n. K/ f z* r; F+ e7 X! o

- |RCC_CFGR_SW //bit01-00[1:0]: 系统时钟源选择。# P( y) `: y, w. u9 b7 G- w

- // 00: Reserved, must be kept at reset value% K, U* U1 c9 [. {

- // 01: HSI16 selected as system clock- F6 [8 L+ v4 O6 P

- // 10: HSE selected as system clock

2 A/ r I4 W) R - /// // 11: PLL selected as system clock2 f! z0 k# j" A6 f

- ;

下面是RCC寄存器:

! y1 g& l% Y3 N8 {

" s% r0 f* J; Z! w$ v- void RCC_Init(void)

+ H( K( v& ~( r - {6 I! F! i' e3 P8 u- J+ a0 ~

- //--------------------------------------------------------------------------------------//

; l6 j" F0 Q, M - //---------------------------------------- AHB1 ----------------------------------------//' c7 @' {& K$ l4 U k- d$ ~

- //--------------------------------------------------------------------------------------//+ s( Z6 h- M2 c, N! D

- RCC->AHB1RSTR |= 0 //default: 0x0000 0000

: W9 C* _$ p; V) v' ~* W+ y. w - // |RCC_AHB1RSTR_CRCRST //bit12( U' Z2 E4 ^* b, e5 s. C0 D

- // |RCC_AHB1RSTR_FLASHRST //bit08

0 A7 s1 t( E/ k9 K5 \( k3 | - // |RCC_AHB1RSTR_FMACRST //bit04

# D( c1 t4 S( S5 a+ T7 f7 u9 ^$ r - // |RCC_AHB1RSTR_CORDICRST //bit03( U3 t- i/ ]9 o$ }& s

- // |RCC_AHB1RSTR_DMAMUX1RST //bit02! _' S0 r) G6 o4 ?$ L% t+ \1 H- a* e

- // |RCC_AHB1RSTR_DMA2RST //bit01# R. J& N8 v1 o/ S4 |. H

- // |RCC_AHB1RSTR_DMA1RST //bit00# K c0 p6 w$ I i! x3 L

- ;

7 A. A ~: Z* H: Z4 g+ m$ Z8 L - RCC->AHB1RSTR &= 0xffffffff //default: 0x0000 0000

1 d, @& i% T b R' R. K - // &~RCC_AHB1RSTR_CRCRST //bit12

; f+ z& Q1 g( ~2 E- r# G& U! j - // &~RCC_AHB1RSTR_FLASHRST //bit08: w2 ? p8 H* o+ i

- // &~RCC_AHB1RSTR_FMACRST //bit04# Z: a( v1 R! X7 R3 T

- // &~RCC_AHB1RSTR_CORDICRST //bit03

5 n% ^# I* b# h& i) u0 p - // &~RCC_AHB1RSTR_DMAMUX1RST //bit02

9 L: p9 m' U* ?( P. |! T - // &~RCC_AHB1RSTR_DMA2RST //bit01

. r( E% U2 b( n/ D0 M; s/ X - // &~RCC_AHB1RSTR_DMA1RST //bit00& d2 V ~0 }: N$ x" x

- ; g; o+ `, t+ ^1 R- A# x3 _; H

-

; Y! }) v# H+ t( v - RCC->AHB1ENR |= 0 //default: 0x0000 0100

! ^- N V1 p7 V' Q7 u4 I - // |RCC_AHB1ENR_CRCEN //bit12

" y8 U \* r: |0 x- Z" k" U - // |RCC_AHB1ENR_FLASHEN //bit08

1 a$ X( g0 `3 G4 ?+ a - // |RCC_AHB1ENR_FMACEN //bit04/ L0 a$ O( W- G& G

- // |RCC_AHB1ENR_CORDICEN //bit03

9 W+ j) u* k# K$ b! w0 | - // |RCC_AHB1ENR_DMAMUX1EN //bit02

0 R1 m7 ]/ w1 | - // |RCC_AHB1ENR_DMA2EN //bit01

1 l0 \1 A+ S. M; G( \/ A - // |RCC_AHB1ENR_DMA1EN //bit00

; v: ^) ?$ y3 B% ^4 s) i - ;% e: W" @( m( p! y9 V# a

- //--------------------------------------------------------------------------------------//! t% a( [) n; q8 s p

- //---------------------------------------- AHB2 ----------------------------------------//

) g; a3 M( B9 b0 q* m- F! } - //--------------------------------------------------------------------------------------//% b8 z9 `+ y. i& j

- RCC->AHB2RSTR |= 0 //defualt: 0x0000 0000

9 C, f6 I: Y; q& @/ E1 I. c - // |RCC_AHB2RSTR_RNGRST //bit26: b6 Z: `- X* M+ m d( K

- // |RCC_AHB2RSTR_RNGRST //bit24

2 R. Q/ i: `: Q, z) \" E# A - // |RCC_AHB2RSTR_DAC4RST //bit19

. U5 k! q- h7 S. q - // |RCC_AHB2RSTR_DAC3RST //bit18

- I7 J, [$ ~$ ]5 a& E1 H" {& |2 p - // |RCC_AHB2RSTR_DAC2RST //bit176 }0 s" ]4 i2 X

- // |RCC_AHB2RSTR_DAC1RST //bit16

q; V2 V% ^# ]- M+ f2 d - // |RCC_AHB2RSTR_ADC345RST //bit14" _3 _8 Y8 F5 b! l; c! G# M

- // |RCC_AHB2RSTR_ADC12RST //bit13

5 r! Y$ \6 K: T - // |RCC_AHB2RSTR_GPIOGRST //bit064 Z) p7 G/ Z6 ]

- // |RCC_AHB2RSTR_GPIOFRST //bit05% ~2 J4 ]% _ ?( `' q6 `

- // |RCC_AHB2RSTR_GPIOERST //bit049 L/ B" n! F1 w. p' j

- // |RCC_AHB2RSTR_GPIODRST //bit03 W3 x* m. h6 t

- |RCC_AHB2RSTR_GPIOCRST //bit025 p% M7 [9 C- |/ O3 U2 y# ]

- // |RCC_AHB2RSTR_GPIOBRST //bit014 w$ w) ~( `; n( Y- p5 Q- e% d

- // |RCC_AHB2RSTR_GPIOARST //bit00& }4 C% O e; h

- ;

8 g9 M/ j0 g, @2 L' P* `5 b6 z2 Z( M - RCC->AHB2RSTR &= 0xffffffff //defualt: 0x0000 0000

4 W9 X3 U0 V5 s( c - // &~RCC_AHB2RSTR_RNGRST //bit26

! s( u6 D; {0 K - // &~RCC_AHB2RSTR_RNGRST //bit246 A0 ]& K% h) d7 c

- // &~RCC_AHB2RSTR_DAC4RST //bit197 q) C* Z$ v, j. R7 V3 n& y

- // &~RCC_AHB2RSTR_DAC3RST //bit18

, D! D U1 D/ K/ {& J ~ V! b - // &~RCC_AHB2RSTR_DAC2RST //bit17

# x0 ^( p+ }, M* i - // &~RCC_AHB2RSTR_DAC1RST //bit16

. ~3 i' i, F1 C* n! ]" X - // &~RCC_AHB2RSTR_ADC345RST //bit14" j0 {" g; O& V7 Z

- // &~RCC_AHB2RSTR_ADC12RST //bit135 p4 A3 Q: S& Y1 P: h* A

- // &~RCC_AHB2RSTR_GPIOGRST //bit06

$ z& j, ]" P! k% I3 o - // &~RCC_AHB2RSTR_GPIOFRST //bit05

1 p/ |# ~9 z/ b9 A3 Z - // &~RCC_AHB2RSTR_GPIOERST //bit04

6 k0 n T8 L8 E1 a4 [! X( G# O - // &~RCC_AHB2RSTR_GPIODRST //bit03

; N6 \. o, A# k2 e/ J( @ - &~RCC_AHB2RSTR_GPIOCRST //bit024 N1 ]- j6 _$ O6 J! H# ^3 w

- // &~RCC_AHB2RSTR_GPIOBRST //bit01

5 T+ y, G$ o6 a) j - // &~RCC_AHB2RSTR_GPIOARST //bit007 B ^, C; L, r7 e7 h$ r

- ;1 I/ I/ h: X1 B' g* a

- RCC->AHB2ENR = 0 //default: 0x0000 0000$ \8 C! t0 F7 G8 ?2 A" {1 f

- // |RCC_AHB2ENR_RNGEN //bit26

5 O1 j/ @' ~& b: U - // |RCC_AHB2ENR_DAC4EN //bit19

% k' c$ J7 x2 a( B8 x3 _ - // |RCC_AHB2ENR_DAC3EN //bit186 p/ u( P4 ^ X/ N

- // |RCC_AHB2ENR_DAC2EN //bit17" {( Z" `$ ~' o3 t: A5 M6 J

- // |RCC_AHB2ENR_DAC1EN //bit16

8 Y0 \5 i1 c6 K; w; q; d: b6 ^ - // |RCC_AHB2ENR_ADC345EN //bit142 d1 J) C) H; e* A

- // |RCC_AHB2ENR_ADC12EN //bit13. |6 D. s1 P3 j( F4 l

- // |RCC_AHB2ENR_GPIOGEN //bit06

1 L& Z+ _6 j5 e% g3 m7 G( M - // |RCC_AHB2ENR_GPIOFEN //bit05; b7 C* O2 t/ ?9 w5 v

- // |RCC_AHB2ENR_GPIOEEN //bit049 j+ X1 g: x1 Z7 ~* k7 a( Y, p

- // |RCC_AHB2ENR_GPIODEN //bit03

( y% H! n- A1 P, ]5 N& n - |RCC_AHB2ENR_GPIOCEN //bit02

; _- g+ C4 S8 r) q, C' U - // |RCC_AHB2ENR_GPIOBEN //bit011 F# O5 \# W) b

- // |RCC_AHB2ENR_GPIOAEN //bit00

% A9 X( r" x; n. [ [ - ;

$ h9 i8 v8 E: o5 K - //--------------------------------------------------------------------------------------//

2 o5 p9 `3 D0 c5 g: w+ a - //---------------------------------------- AHB3 ----------------------------------------//

; R& G0 E. @3 h; [% b - //--------------------------------------------------------------------------------------//

4 {3 P* o5 ]) p. M - RCC->AHB3RSTR |= 0 //default:0x0000 00007 k8 m# i5 ~/ m8 x6 O

- // |RCC_AHB3RSTR_QSPIRST //bit08

3 Y5 w# A6 U& o6 v7 D - // |RCC_AHB3RSTR_FMCRST //bit00( k, B$ n- A6 @! M# E5 f

- ;

/ V3 n2 P6 h: S3 n0 c& y: [ - RCC->AHB3RSTR &= 0xffffffff //default:0x0000 0000

2 r6 v, @7 O1 V. l+ \8 Q0 w - // &~RCC_AHB3RSTR_QSPIRST //bit08; a/ O$ j) Y% q+ N+ N8 I# @

- // &~RCC_AHB3RSTR_FMCRST //bit00% f% x! Y8 F4 W& w" T

- ;$ L9 t5 \( _+ A, ^( e

! ]. [8 z x3 e9 l o- RCC->AHB3ENR |= 0 //default: 0x0000 0000! r0 b9 i- F! r' q4 H

- // |RCC_AHB3ENR_QSPIEN //bit08# m- q1 a/ w+ @: \! d) D$ z& |

- // |RCC_AHB3ENR_FMCEN //bit00' q' R9 ~# `* I3 c3 C8 t

- ;

2 ]3 y: ^7 h- | - //--------------------------------------------------------------------------------------//

6 U: ^5 r1 E3 K5 b - //---------------------------------------- APB1 ----------------------------------------//

' ~4 a0 j1 R4 P8 s - //--------------------------------------------------------------------------------------//0 x$ P( d o+ R4 J( A

- RCC->APB1RSTR1 |= 0 //default: 0x0000 00008 `5 k: [: a1 F9 f6 Q4 Q

- // |RCC_APB1RSTR1_LPTIM1RST //bit31

% r2 ~' d3 A. Q/ D# e8 P2 d - // |RCC_APB1RSTR1_I2C3RST //bit30: F' P4 I, e9 v4 M) `7 J. t) }! D

- // |RCC_APB1RSTR1_PWRRST //bit289 D% f5 a2 l$ R8 z W

- // |RCC_APB1RSTR1_FDCANRST //bit25% E+ X* t% k) ~9 t

- // |RCC_APB1RSTR1_USBRST //bit23% Y. E& U; |7 S! l% D8 b

- // |RCC_APB1RSTR1_I2C2RST //bit22/ P* ~3 @0 W* |

- // |RCC_APB1RSTR1_I2C1RST //bit21+ q4 |" e* s- ~5 M

- // |RCC_APB1RSTR1_UART5RST //bit20; l4 n& v& ]( q8 j5 N

- // |RCC_APB1RSTR1_UART4RST //bit19+ w6 |$ a* r6 k

- // |RCC_APB1RSTR1_USART3RST //bit18# _# ^+ H& I2 E0 \4 u2 N

- // |RCC_APB1RSTR1_USART2RST //bit17# A- `7 F& l: ]) l2 }

- // |RCC_APB1RSTR1_SPI3RST //bit152 z' r* _- u* \8 [0 m( E# O

- // |RCC_APB1RSTR1_SPI2RST //bit14 P: n. M& v4 J1 S

- // |RCC_APB1RSTR1_CRSRST //bit08: ~/ c! g, ]' b1 A9 f

- |RCC_APB1RSTR1_TIM7RST //bit05

! k7 M6 S, C) a. h - // |RCC_APB1RSTR1_TIM6RST //bit04- A- C! I' B7 X& W% Z+ G' i

- // |RCC_APB1RSTR1_TIM5RST //bit03% F+ F% D! a* J

- // |RCC_APB1RSTR1_TIM4RST //bit02

" t" @ I. X; T4 C: x' E7 ^9 k - // |RCC_APB1RSTR1_TIM3RST //bit01$ j+ ~, l1 d9 ?' _

- // |RCC_APB1RSTR1_TIM2RST //bit006 e0 \3 Z& U+ |0 o

- ;. R+ }- {4 I! o! H

- RCC->APB1RSTR1 &= 0xffffffff//default: 0x0000 0000

* Q% g+ e* N2 N( ^( l# s* Y% p2 U! X - // &~RCC_APB1RSTR1_LPTIM1RST //bit31, ]9 N& X4 q8 D# A1 z7 l2 `8 C

- // &~RCC_APB1RSTR1_I2C3RST //bit30, } I; P* B6 @) a; h! M/ O$ s; H

- // &~RCC_APB1RSTR1_PWRRST //bit28

, X! S+ _5 @. w. K0 V' J3 { - // &~RCC_APB1RSTR1_FDCANRST //bit257 p9 I, D. a$ P- g$ r

- // &~RCC_APB1RSTR1_USBRST //bit23

: ]/ X4 o4 }& B) C% N$ z - // &~RCC_APB1RSTR1_I2C2RST //bit22* r$ z5 ^5 O4 J; g7 Y

- // &~RCC_APB1RSTR1_I2C1RST //bit21+ r6 I2 }4 f% p! _- Z0 g$ S5 f

- // &~RCC_APB1RSTR1_UART5RST //bit20; ^+ }7 D; s' l$ S

- // &~RCC_APB1RSTR1_UART4RST //bit194 I! P7 |1 G; s$ k

- // &~RCC_APB1RSTR1_USART3RST //bit18# n" r0 G5 p; n

- // &~RCC_APB1RSTR1_USART2RST //bit17, K& O5 S0 M: E- Z/ b

- // &~RCC_APB1RSTR1_SPI3RST //bit15

3 f$ n$ n% l$ U r8 Z t- A. O$ m: a9 T - // &~RCC_APB1RSTR1_SPI2RST //bit14* P; A$ Q' w) C& s5 E* f; c7 M1 l

- // &~RCC_APB1RSTR1_CRSRST //bit08* s0 T' s: B! N2 F" ^ b

- &~RCC_APB1RSTR1_TIM7RST //bit057 E5 E- J6 u7 ~- X

- // &~RCC_APB1RSTR1_TIM6RST //bit04

* f2 C0 j7 B6 n - // &~RCC_APB1RSTR1_TIM5RST //bit03- c3 }& V& L) m; d9 u6 q7 D

- // &~RCC_APB1RSTR1_TIM4RST //bit02, ?: x2 F+ M+ W5 R" j+ b# v

- // &~RCC_APB1RSTR1_TIM3RST //bit01# } u) s6 K+ V* i+ S& X

- // &~RCC_APB1RSTR1_TIM2RST //bit00

. T* |% ~3 x8 V0 \4 V( Z - ;

$ r6 [/ c: V! a

- q& G+ s% J$ k% [: _ B7 J9 ?1 t- RCC->APB1ENR1 |= 0 //default: 0x0000 0400

' s' [( r! f0 i) b8 } L4 K+ | - // |RCC_APB1ENR1_LPTIM1EN //bit31& ^3 f$ B. O9 ^- Z8 s6 U

- // |RCC_APB1ENR1_I2C3EN //bit30& n9 m5 D7 W/ O: P1 z% c/ u

- // |RCC_APB1ENR1_PWREN //bit28, V* [9 O, V4 o+ w, K i6 [

- // |RCC_APB1ENR1_FDCANEN //bit25

2 `& r! r3 y, ]$ a3 g- [ - // |RCC_APB1ENR1_USBEN //bit23

# [, w, _# W' I r - // |RCC_APB1ENR1_I2C2EN //bit22

: C* g( a, U4 C0 D% g - // |RCC_APB1ENR1_I2C1EN //bit21

! o# f7 x6 Y9 G, w. {! M - // |RCC_APB1ENR1_UART5EN //bit20" ~/ r( O! F) P

- // |RCC_APB1ENR1_UART4EN //bit19

K5 }, T8 |3 b# q - // |RCC_APB1ENR1_USART3EN //bit18

7 [. U& C8 V& [% ] - // |RCC_APB1ENR1_USART2EN //bit17

% ^, } o4 `( G% x: o! | - // |RCC_APB1ENR1_SPI3EN //bit153 m# M! q2 A+ e0 ]

- // |RCC_APB1ENR1_SPI2EN //bit14

- p: n8 I `" q u7 C - // |RCC_APB1ENR1_WWDGEN //bit11

# b# I7 s& }+ K9 |/ q+ c) ^2 k - // |RCC_APB1ENR1_RTCAPBEN //bit10$ v! d/ q. O# H2 s# C

- // |RCC_APB1ENR1_CRSEN //bit08

7 H" f ~; u0 A# k0 O( Q - |RCC_APB1ENR1_TIM7EN //bit05& q4 U+ ?2 d7 B& @9 s# N/ A

- // |RCC_APB1ENR1_TIM6EN //bit04

: v2 p' B" J/ C! e - // |RCC_APB1ENR1_TIM5EN //bit03

5 X9 ^ n8 I6 d5 m - // |RCC_APB1ENR1_TIM4EN //bit02! {9 i) c" T4 U6 J7 H! A

- // |RCC_APB1ENR1_TIM3EN //bit01

* [$ d- C& g6 I/ v" z$ v* I% I - // |RCC_APB1ENR1_TIM2EN //bit00" y" {" t1 Y. e+ K

- ;

2 D& z0 |& F- K1 A, T! p0 F

/ F6 M1 T$ z' g- ' `7 @* A, I$ d) _

- RCC->APB1RSTR2 |= 0 //default: 0x0000 00006 g8 T+ p' K6 ]9 e

- // |RCC_APB1RSTR2_UCPD1RST //bit08

0 `: z6 n8 ]8 b' s - // |RCC_APB1RSTR2_I2C4RST //bit01

' I" N2 _2 \" a+ Q8 c% B$ ~ - // |RCC_APB1RSTR2_LPUART1RST //bit00: s2 s* h: C9 i$ G

- ;$ O2 @" M* B |) ]# N. [1 e

- RCC->APB1RSTR2 &= 0xffffffff//default: 0x0000 0000' Q# W2 Z1 B' D0 @& w

- // &~RCC_APB1RSTR2_UCPD1RST //bit08

! r/ p* h z% o - // &~RCC_APB1RSTR2_I2C4RST //bit01: |+ D2 A6 s: m4 X: G4 N

- // &~RCC_APB1RSTR2_LPUART1RST //bit00

% d+ ~4 y8 c" @ r- o$ q - ;

' u, R" G6 ^$ U' J [9 m! U! ?# c

& h5 {) ^2 M8 Q8 U/ R- RCC->APB1ENR2 |= 0 //default: 0x0000 0000% V8 C$ V. ^5 ?, I

- // |RCC_APB1ENR2_UCPD1EN //bit08

_) M2 ]$ j& _+ S T+ F2 U - // |RCC_APB1ENR2_I2C4EN //bit01

/ L! n8 g, n4 v" h8 y - // |RCC_APB1ENR2_LPUART1EN //bit00

) k) s# n$ `; L - ;

3 V% z* C |8 p - //--------------------------------------------------------------------------------------//2 e$ q- s9 k! @# V

- //---------------------------------------- APB2 ----------------------------------------//: c# j- T, A1 v7 ^- R' F8 s

- //--------------------------------------------------------------------------------------//- Z5 f9 S- p6 s2 d) A, k2 `. C+ @

- RCC->APB2RSTR |= 0 //default: 0x0000 0000

* N* F8 m! `; y/ A! D - // |RCC_APB2RSTR_HRTIM1RST //bit26

! z& T) K; X9 G9 K B# g - // |RCC_APB2RSTR_SAI1RST //bit21

/ P& A6 j4 L# p- u# n& h- T - // |RCC_APB2RSTR_TIM20RST //bit20

( u; Y2 E* x3 S8 ^+ t2 z - // |RCC_APB2RSTR_TIM17RST //bit18, t: x5 z* B% M* U+ I+ w2 ^5 v: N0 Q

- // |RCC_APB2RSTR_TIM16RST //bit176 H+ J5 w4 v8 I: ^

- // |RCC_APB2RSTR_TIM15RST //bit16+ m% N7 x& Z2 t) R/ Q/ a

- // |RCC_APB2RSTR_SPI4RST //bit151 Z$ |7 j0 j0 `

- // |RCC_APB2RSTR_USART1RST //bit14

( F3 E( i$ o9 i$ F6 l x - // |RCC_APB2RSTR_TIM8RST //bit13- e! {2 F- @ P8 g1 N

- // |RCC_APB2RSTR_SPI1RST //bit12

9 i; A2 r) i' _6 r6 p - // |RCC_APB2RSTR_TIM1RST //bit11

, ], r! X9 J* d, E6 i. C2 s - // |RCC_APB2RSTR_SYSCFGRST //bit00% s% m0 p3 _2 z6 { T

- ;

' r6 g. `' r2 i ] m" O - RCC->APB2RSTR &= 0xffffffff //default: 0x0000 0000

8 K" v, |; T/ d' W - // &~RCC_APB2RSTR_HRTIM1RST //bit26

3 X* y' l/ I! K2 d - // &~RCC_APB2RSTR_SAI1RST //bit21

3 c$ E3 R* j9 I2 W: k - // &~RCC_APB2RSTR_TIM20RST //bit20* x- I& R% ?6 Z1 ^0 {

- // &~RCC_APB2RSTR_TIM17RST //bit18. R! E8 v! Z, E

- // &~RCC_APB2RSTR_TIM16RST //bit17

8 |* r0 d* k! w# W1 F" v - // &~RCC_APB2RSTR_TIM15RST //bit16

: Z1 x& k% S9 N4 v. e1 C - // &~RCC_APB2RSTR_SPI4RST //bit15

$ ~$ ]( z8 B( Q+ l2 g1 }0 I& n - // &~RCC_APB2RSTR_USART1RST //bit14

/ U& J0 X( ]# K6 z - // &~RCC_APB2RSTR_TIM8RST //bit13

0 t8 T1 P5 C# y- p8 X5 v - // &~RCC_APB2RSTR_SPI1RST //bit12

/ d6 _% ?6 ?$ z& j! m! U - // &~RCC_APB2RSTR_TIM1RST //bit11

8 E$ w0 X4 `' y7 v! S - // &~RCC_APB2RSTR_SYSCFGRST //bit00

: M9 o; Y' ~9 i - ;/ Q! Q! G: y* B! y

- ! x0 ~0 D4 Z+ i: J

- RCC->APB2ENR |= 0 //default: 0x0000 00009 Y) L p( n& b! j% X6 B# A' `" s

- // |RCC_APB2ENR_HRTIM1EN //bit26

, u3 g/ L, E# |6 ?4 ` - // |RCC_APB2ENR_SAI1EN //bit21

0 G7 o. m3 O8 ?9 U# B4 N1 }8 B - // |RCC_APB2ENR_TIM20EN //bit20

' c7 g; q) @' B5 H: l - // |RCC_APB2ENR_TIM17EN //bit18

4 O1 W$ C; y8 \: ]/ k7 c% ` - // |RCC_APB2ENR_TIM16EN //bit17

+ |; L: A" h8 t$ R2 f' ? - // |RCC_APB2ENR_TIM15EN //bit16

! I* K9 D- B: g& s4 t - // |RCC_APB2ENR_SPI4EN //bit15/ r& i) W4 _2 p* @- ^

- // |RCC_APB2ENR_USART1EN //bit14. R; ~- b- u# U, l

- // |RCC_APB2ENR_TIM8EN //bit13

, _& A9 J$ K9 t" V, R& _- i- u7 y - // |RCC_APB2ENR_SPI1EN //bit122 A, D7 l+ n) }+ @0 [

- // |RCC_APB2ENR_TIM1EN //bit11 Y* x5 _& S: l3 o: Y& u

- // |RCC_APB2ENR_SYSCFGEN //bit00, g- p) a/ b4 ~: |

- ;

( X! H$ S' E% Y0 ]9 r( ? - }

X* Q( r( |' l' H! A5 L

& Q% K n4 Q! ^+ C+ N) l5 Q" M. S4 e* k! Z

3 P7 f* C, t6 H: Y% |7 L! @

: P% T' m, g, P

|