|

STM32F413/423单片机参考手册 前言 $ ]( [' U y% C# M% a% | 5 C' S3 q" }$ V# \ 本参考手册面向应用开发人员, 提供有关使用 STM32F413/423 微控制器存储器与外设的完整信息。 STM32F413/423 构成一个微控制器系列,各产品具有不同的存储器大小、封装和外设。有关订购信息以及器件的机械与电气特性,请参见数据手册。 2 r$ W: j5 i; e. X ) ]& y' d2 Q) o# i 有关 Arm® 带 FPU 的 Cortex®-M4 内核的信息,请参见Cortex®-M4 技术参考手册。 相关文档意法半导体网站 www.st.com 提供以下文档: 4 g3 i0 ^7 V9 ]# B 0 c1 z1 w5 W0 ~% q. K

1 文档约定 4 y& ]$ ?2 P- u3 j1 K1 T$ j1 N9 m 1.1 一般信息 , r m9 c+ b: r9 @3 _3 e& h1 u STM32F413/423 器件具有 Arm®(a) Cortex®-M4 with FPU 内核, [& @' W0 S/ `; w- v6 F! F/ q& S0 r 1.2 寄存器相关缩写词列表 4 U& |2 j& g- x) P! U 寄存器说明中使用以下缩写词(b): 6 Q# Y1 g$ P, M1 j" p6 Z' T / n' R# \' V* @$ Q 读/写 (rw) 软件可以读写该位。 只读 (r) 软件只能读取该位。 只写 (w) 软件只能写入该位。读取该位时将返回复位值。 - R, ~" p9 m! E8 e 读取/写入 0 清零 (rc_w0) 软件可以通过读取该位,也可以通过写入 0 将该位清零。写入 1 对该位的值无影响。 读取/写入 1 清零 (rc_w1) 软件可以通过读取该位,也可以通过写入 1 将该位清零。写入 0 对该位的值无影响。 读取/写入清零 (rc_w) 软件可以通过读取该位,也可以通过写入寄存器将该位清零。写入该位的值并不重要。 读取/读取清零 (rc_r) 软件可以读取该位。读取该位时,将自动清零。写入该位对其值无影响。 * D0 ~$ X: l$ ?4 h- w7 [1 U 读取/读取置位 (rs_r) 软件可以读取该位。读取该位时,将自动置位。写入该位对其值无影响。 读取/置位 (rs) 软件可以读取该位,也可将其置 1。写入 0 对该位的值无影响。 读/仅可写入一次 (rwo) 软件仅可写入一次该位,但可随时读取该位。只能通过复位将该位返回到复位值。 切换 (t) 软件可以通过写入 1 来切换该位。写入 0 无影响。 只读写触发 (rt_w1) 软件可以读取该位。写入 1 时,将触发事件,但不会影响该位的值。 5 c! N( Z( k0 K7 G2 ~" K 保留 (Res.) 保留位,必须保持复位值。) [+ `$ u+ w: |# ^0 C( w1 p 1.3 词汇表 本节简要介绍本文档中所用首字母缩略词和缩写词的定义: 7 F5 D5 V9 \1 L% ~1 C- a0 e

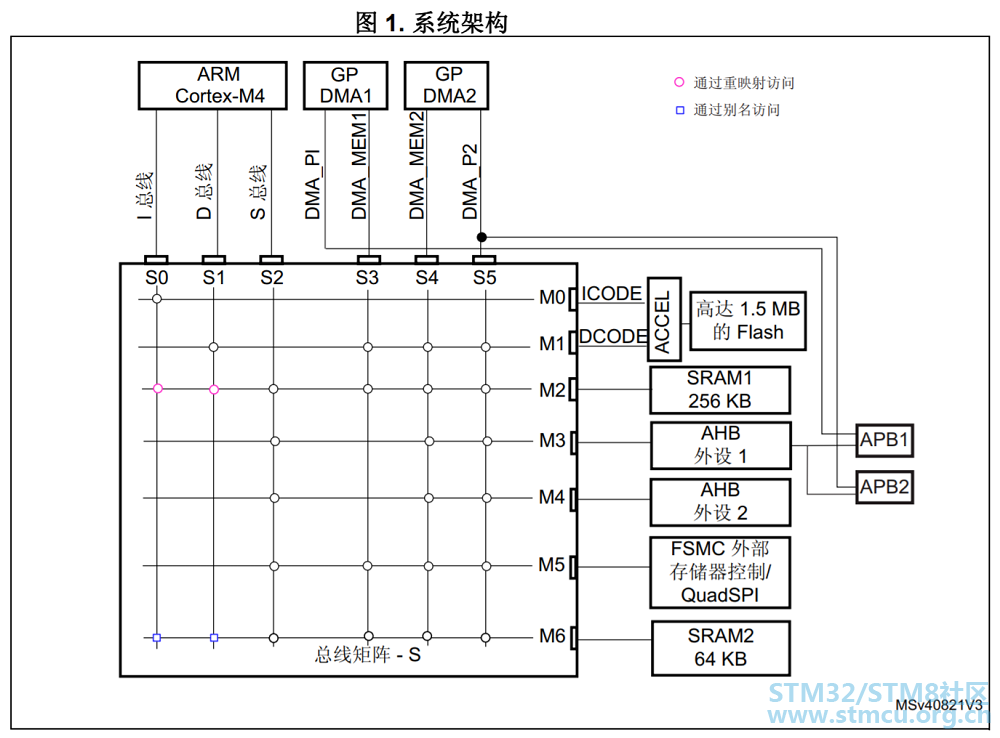

1.4 外设可用性 有关各型号产品的外设可用性及数量的信息,请参见特殊器件数据手册。 2 系统和存储器概述 2.1 系统架构 STM32F413/423 的主系统由 32 位多层 AHB 总线矩阵构成,可实现以下部分的互连: 5 \6 w" y' W2 y# i- S 六条主控总线: – 带 FPU 的 Cortex®-M4内核 I 总线、D 总线和 S 总线 }- n& }" s; l- o/ n& ~, Q: V – DMA1 存储器总线 6 q) r3 p0 } J; S – DMA2 存储器总线 – DMA2 外设总线 5 V4 Z! y7 v7 g2 B 七条被控总线: q7 ]" l% h. K& L( J; x; k z! R0 a – 内部 Flash ICode 总线 5 s5 M4 R3 E/ x – 内部 Flash DCode 总线 – 主内部 SRAM1 (256 KB) - r4 J w7 y' l, @5 K – 辅助内部 SRAM2 (64 KB) – AHB1 外设(包括 AHB-APB 总线桥和 APB 外设) – AHB2 外设 : H* e: |: p( W0 O) a – FSMC/QuadSPI 6 [9 }1 W' E$ k0 q; d. {2 x 借助总线矩阵,可以实现主控总线到被控总线的访问,这样即使在多个高速外设同时运行期间,系统也可以实现并发访问和高效运行。此架构如图 1 所示。 # S, R- y* B* W: o- J/ z

2.1.1 I 总线 此总线用于将带 FPU 的 Cortex®-M4 内核的指令总线连接到总线矩阵。内核通过此总线获取指令。此总线访问的对象是包含代码的存储器(内部 Flash/SRAM1/SRAM2)。 2.1.2 D 总线 此总线用于将带 FPU 的 Cortex®-M4 的数据总线连接到总线矩阵。内核通过此总线进行立即数加载和调试访问。此总线访问的对象是包含代码或数据的存储器(内部 Flash/SRAM1/SRAM2)。 9 @% l8 N; b: |, _2.1.3 S 总线 此总线用于将带 FPU 的 Cortex®-M4 内核的系统总线连接到总线矩阵。此总线用于访问位于外设、SRAM1 或 SRAM2 中的数据。也可通过此总线获取指令(效率低于 ICode)。此总线访问的对象是内部 SRAM1/SRAM2、包括 APB 外设在内的 AHB1 外设、AHB2 外设和外部存储器(通过外设接口 FSMC 和 QUADSPI)。 ; R( y/ I) h% y* x! M8 K! s" K# J% \- @9 \3 d8 D- d / [7 Q$ m/ U8 L7 t9 Z7 P % R9 J, P( c8 X, c& } |

STM32固件库分享,超全系列整理

【中文文档】AN3965_STM32F40x和STM32F41x基于串口的IAP

STM32F4-DISC 实现USB主机(U盘)和USB设备(虚拟串口)自动切换

STM32F4中文用户手册

基于STM32F407的FreeRTOS阶段性的总结(13)

STM32F400、STM32F402 Cortex-M4超值单片机

基于STM32F407的FreeRTOS获取各任务运行时间及占用情况(4)

基于STM32F407的FreeRTOS任务的挂起与恢复(3)

基于STM32F407的FreeRTOS任务的创建与删除经验分享(2)

基于STM32F407的FreeRTOS环境搭建经验分享(1)