|

STM32L4Rxxx和STM32L4Sxxx单片机参考手册* s5 _1 J4 _2 _5 j: q! W& P 前言 本参考手册面向应用开发人员,提供有关使用 STM32L4Rxxx 和 STM32L4Sxxx 微控制器存 储器与外设的完整信息。 " h( n0 C: \, L H! y; h STM32L4Rxxx 和 STM32L4Sxxx 构成微控制器系列,各产品具有不同的存储器大小、封装和 外设。 有关订购信息以及器件的机械与电气特性,请参见相应的数据手册。 ! H+ V" T' E2 D+ @$ E3 k 有关 Arm® Cortex®-M4 内核的信息,请参见 Cortex®-M4 技术参考手册。6 o M5 o: g# ]* u# m! b " B' N, P+ T' D5 |( p- l$ { 相关文档

1 文档约定 9 A5 g) c0 Y" p, A6 I6 ^7 i 6 J$ q6 h7 Q& N7 G8 ]/ `8 V 1.1 寄存器相关缩写词列表 - g" l$ i2 E2 h: @7 t/ ] 寄存器说明中使用以下缩写词(a): + E4 f5 t! E3 R 读/写 (rw) 软件可以读写该位。 只读 (r) 软件只能读取该位。 只写 (w) 软件只能写入该位。读取该位时将返回复位值。 : }9 I! H$ T: ]% I O 读取/写入 0 清零 (rc_w0) 软件可以读取该位,也可以通过写入 0 将该位清零。写入 1 对该位的值无 影响。 K. d, _! u) K; ]1 W 读取/写入 1 清零 (rc_w1) 软件可以读取该位,也可以通过写入 1 将该位清零。写入 0 对该位的值无 影响。 1 s+ |. j( E' v. D4 @ 读取/写入清零 (rc_w) 软件可以读取该位,也可以通过写入寄存器将该位清零。写入该位的值并 不重要。 l0 ?4 A8 z* B/ \ 读取/读取清零 (rc_r) 软件可以读取该位。读取该位时,将自动清零。写入该位对其值无影响。 : ^# D1 q) @; t1 { 读取/读取置位 (rs_r) 软件可以读取该位。读取该位时,将自动置 1。写入该位对其值无影响。 2 F6 [8 T" u0 Z( s- i6 J i 读取/置位 (rs) 软件可以读取该位,也可将其置 1。写入 0 对该位的值无影响。 读/仅可写入一次 (rwo) 软件仅可写入一次该位,但可随时读取该位。只能通过复位将该位返回到 复位值。 切换 (t) 软件可以通过写入 1 来切换该位。写入 0 无影响。 只读,写触发 (rt_w1) 软件可以读取该位。写入 1 时,将触发事件,但不会影响该位的值。 % a8 T3 q4 w% M 保留 (Res.) 保留位,必须保持复位值。 - S% Q9 b/ y A( v9 q5 h2 _ 1.2 词汇表 4 X$ j8 a6 l5 N8 l 本节简要介绍本文档中所用首字母缩略词和缩写词的定义:

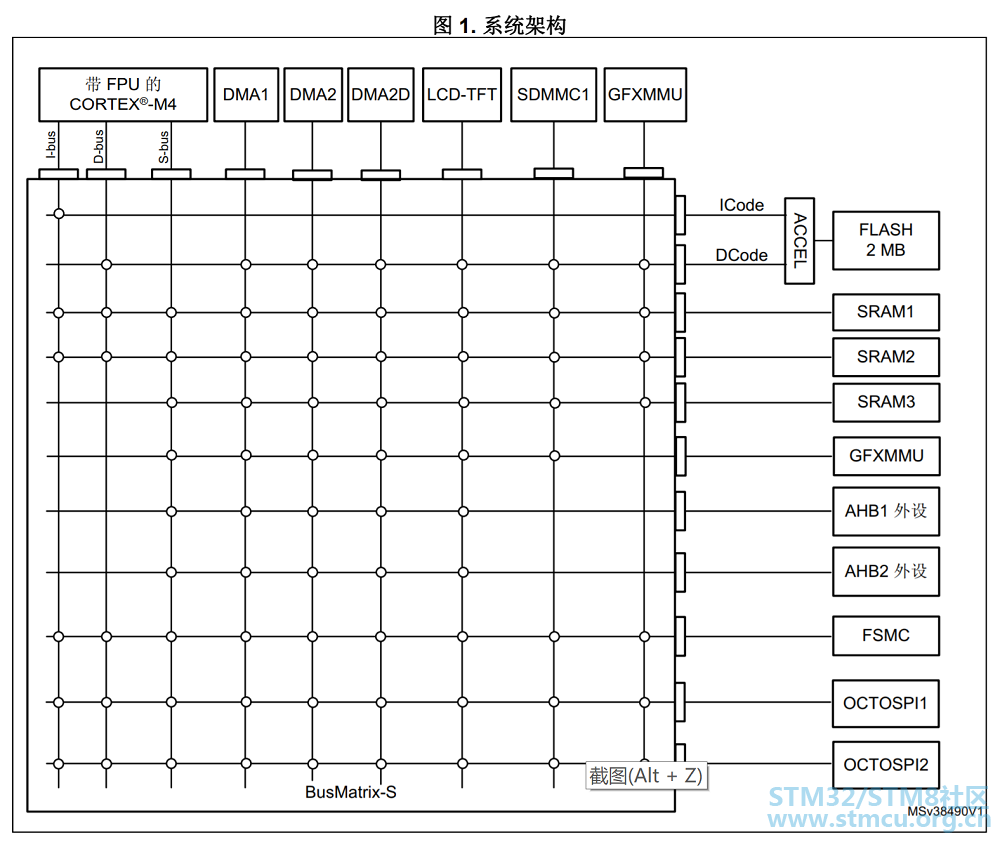

1.3 外设可用性 + E8 h2 X9 y! b. X' w; z! { 有关各型号产品的外设数量意义可用性信息,请参见相关器件数据手册。7 R. O3 U$ ^2 M: j/ ^+ j( r 2 系统和存储器概述 2.1 系统架构 主系统由 32 位多层 AHB 总线矩阵构成,可实现以下部分的互连 最多九条主控总线: – Cortex®-M4(带 FPU 内核 I 总线) + |0 w7 ~& q4 w9 w# I( G – Cortex®-M4(带 FPU 内核 D 总线) . }" ?4 o4 G9 G1 R4 }/ H0 j/ y; H – Cortex®-M4(带 FPU 内核 S 总线) – DMA1 1 K! M5 R! u6 i$ ?/ O – DMA2 – DMA2D(Chrom-Art 加速器™)存储器总线 5 V- q# _2 g/ A2 D- g – LCD-TFT 控制器 DMA 总线 – SDMMC1 总线 – GFXMMU (Chrom-GRC™) 总线 $ { n0 z7 }7 Q3 N E/ X 最多十一条被控总线: l" q; C* @6 h! g/ k* { – ICode 总线上的内部 Flash – DCode 总线上的内部 Flash – 内部 SRAM1 (192 KB) – 内部 SRAM2 (64 KB) 0 H6 I: v/ A4 c – 内部 SRAM3 (384 KB) : G3 C3 ? o8 y0 i – GFXMMU (Chrom-GRC™) : _( L7 A; J3 c$ r+ H! q – AHB1 外设(包括 AHB-APB 总线桥和 APB 外设(连接到 APB1 和 APB2)) – AHB2 外设 & Z! A4 c) F4 y7 d/ B – 灵活存储控制器 (FMC) / n7 m# j/ l8 _ – OCTOSPI1 ; U/ T0 t$ i5 T' Z& }( r3 j. B+ |) O – OCTOSPI2 " C: R! V9 c1 K5 H* F: N1 t6 I 借助总线矩阵,可以实现主控总线到被控总线的访问,这样即使在多个高速外设同时运行期间,系统也可以实现并发访问和高效运行。此架构如图 1 所示: # M& I9 a2 Z, v: E* a$ G, [

|

| 非常感谢 |

| 感谢 |

基于STM32L4R9 的QuadSPI Flash 通讯速率不理想经验分享

STM32L4超低功耗功能概述

基于STM32L431RC Standby和RTC中断唤醒经验分享

基于STM32L431的睡眠模式经验分享

STM32L4R9 的 QuadSPI Flash 通讯速率不理想

STM32L4、STM32L4+和STM32G4系列 微控制器上的专利代码读取保护

STM32L433在STOP模式USART不能工作的解决办法

【实测教程】基于STM32L4系列的实测教程分享合集

STM32L4系列MCU的五种振荡器和使用说明

【实测教程】STM32CubeMX-STM32L4之研究串口通信(printf)