|

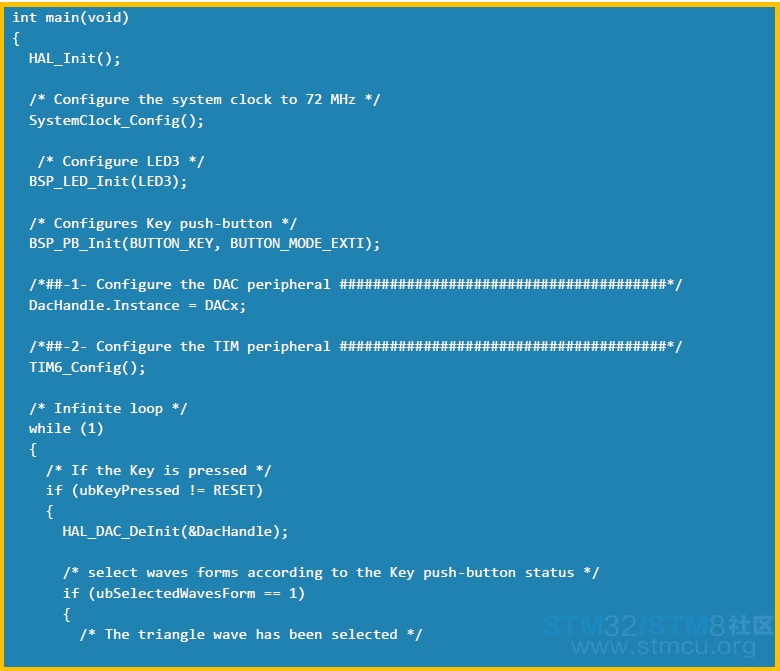

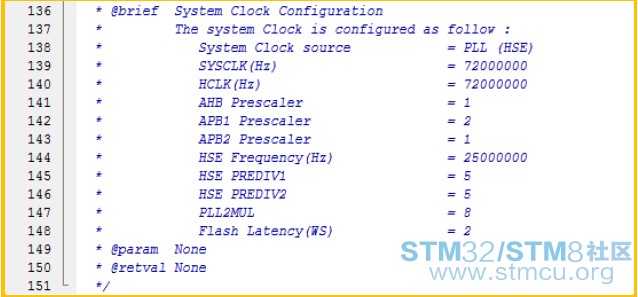

STM32 F1系列 DAC的示例详解 X$ S% N! @5 z/ O$ y. b* n前言 基于学习的目的,详细讲解关于Cube库中的DAC的功能。本次介绍DAC。 ^, k( }2 A7 ]: u7 ^; V6 | " u, w+ Q# T6 U2 W 一、示例详解. K& L) n8 B$ h$ B" a7 A 基于硬件平台:STM32F10C-EVAL,MCU的型号是STM32F107VCT6。 软件则是其Cube库,路径:STM32Cube\Repository\STM32Cube_FW_F1_V1.3.0\Projects\STM3210C_EVAL\Examples\DAC\DAC_SignalsGeneration。- Z0 m, |1 m1 F/ S 1、主程序 软件配置,运行程序可以发现,系统时钟设置为72MHz,定时器使用到的是TIM6;/ x! D) u6 V3 ^

根据时钟树的图谱及其程序, 该示例选择的是内部时钟源作为定时器的时钟源;TIM6的时钟源来自APB1的分频。/ `: R1 X% Y$ ^. Q

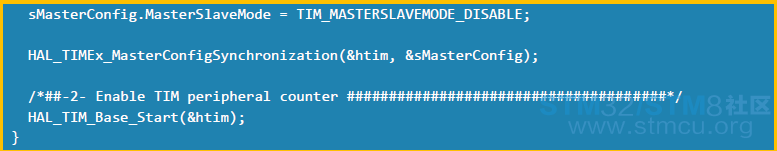

AHB 时钟 (HCLK)在RCC_CFGR寄存器中的分频系数HPRE的值为0,即SYSCLK not divided,即/1,所以HCLK就是72MHz; APB1的prescaler的系数是PPRE1:0x4,HCLK divided 2,即/2,APB1CLK为36MHz;由于APB1的prescaler系数部分频,即/4,所以倍频器起作用,即为上图中的TIMxCLK = 72Mhz。9 K+ T3 i/ a- x& I4 L: A% } 2、 定时器Tim6

设置的是向上计数,周期是0x7FF(2047),从0开始计数到2047,所以该定时器的更新周期:(2047+1)/72 = 28us,' [- U3 w' O0 G/ a: I- {1 O: O. T3 _

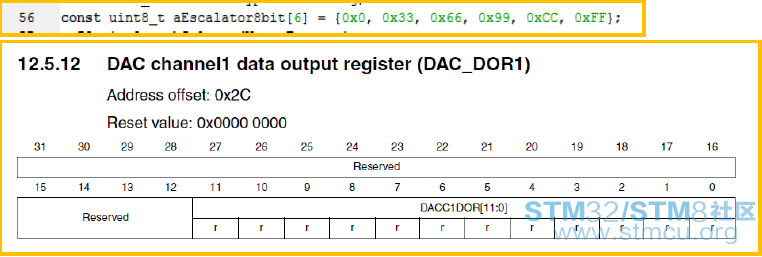

所以传输的6个数值:2 Q5 V3 ?' O+ M( D9 h

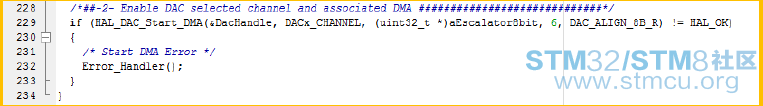

对于8位的DAC,程序中设定的是右对齐,

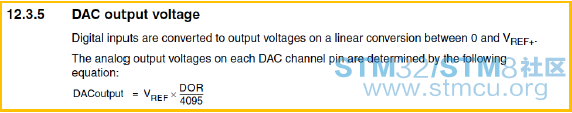

所以,对应的DOR分别为; ~. K5 w. m0 s( d, G6 ` 0x000(0), 0x330(816), 0x660(1632), 0x990(2448), 0xCC0(3264), 0xFF0(4080) ;: z7 K9 x' y+ u) O' w3 Z9 Y D 而Vref = 3.3V, 所以:( o) e5 W7 B1 f) `& I8 o. {: E Vdac 分别等于:也是约在0V; 0.66V; 1.32V; 1.98V; 2.64V; 3.3V之间;2 R' b5 `( |9 e# [: T 3、阶梯波形

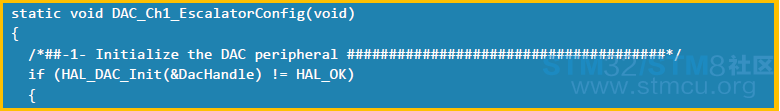

对于阶梯波形比较简单:$ I7 a+ b. \, p: V C! ? 就是上述的6个数值每个28us触发DMA传输一次到DOR的寄存器;% Y: F" y$ U3 P7 c3 s1 Z" l 所以测得的实际波形(6个梯阶,电压分别0V; 0.66V; 1.32V; 1.98V; 2.64V; 3.3V; 周期28*6 = 168us);8 ?2 E1 ]4 s. O4 c: K; i+ C 验证的波形如下:9 d' {; J; ]/ X' U2 s. R+ y

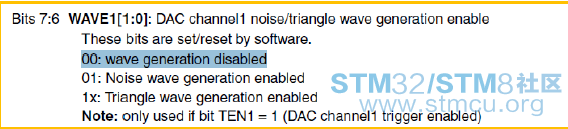

对于阶梯波形的产生,WAVE设置的是0x00;即:wave generation disable;1 S3 x; q5 v$ Y

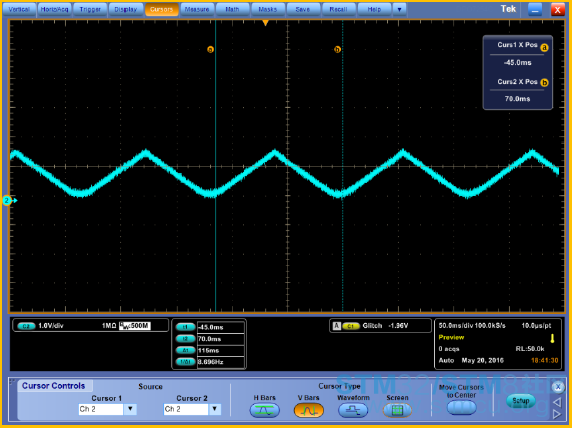

4、三角波 7 X; F: U k0 _$ [8 H

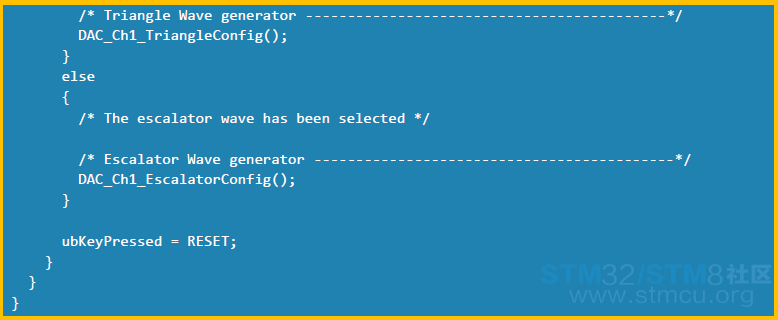

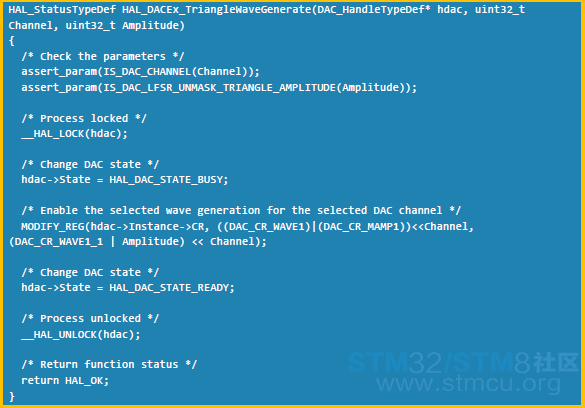

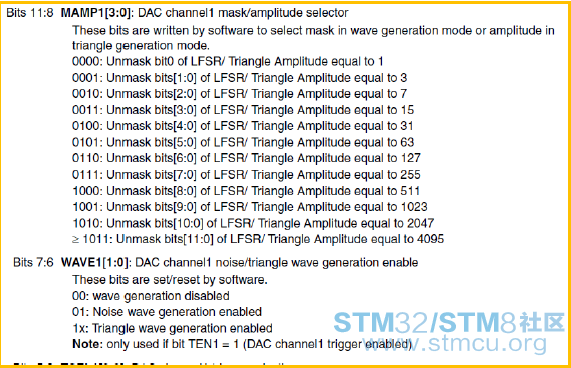

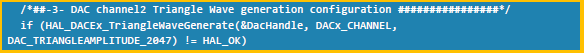

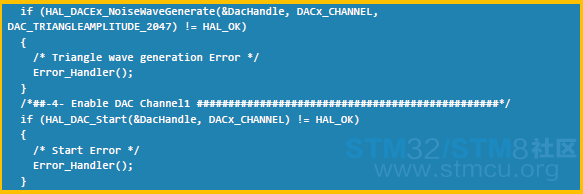

产生三角波的主要代码如上,其实也就是下面的这一段代码:

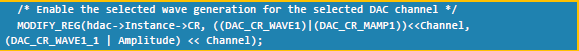

其实也就是设置下面的寄存器的比特位;2 X/ e: r* \( k b# g

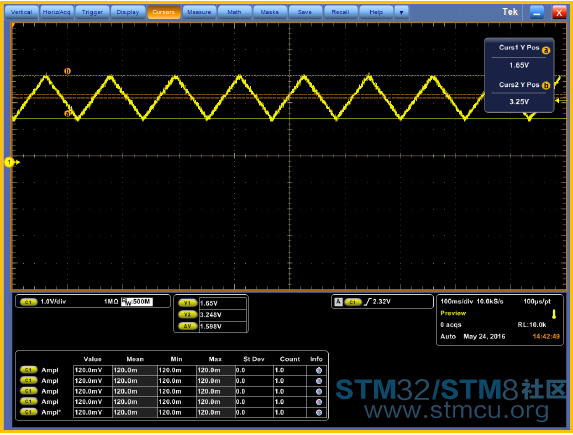

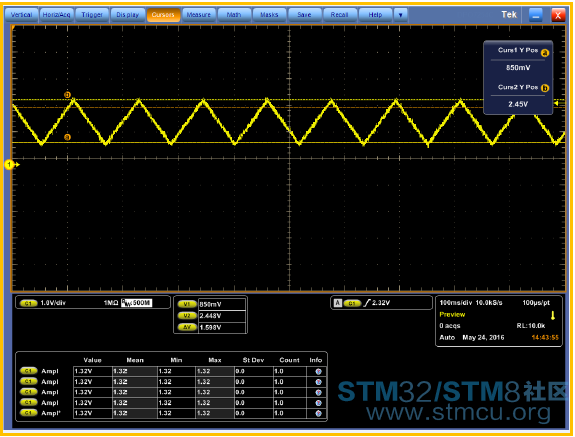

最大的振幅是3.3V,即对应的是4095, 软件里面设置的2047,所以振幅是大约1.65V

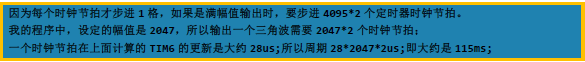

该三角波的产生是由单片机的硬件产生的,软件控制的是:振幅和周期; 振幅通过上述寄存器中的MAMP1来控制;8 m! e5 L2 g. ~ 周期则是定时器Tim6的触发事件? 但是这里的周期并不是128us啊? 改变幅值也会改变三角波的周期的,( S7 k" e5 k9 r, M* Y2 Z5 \$ U 那么这幅值和周期以及定时器之间三者的关系如何呢? 答案: ' D2 h$ H2 I; R

符合推论。9 n/ c: ]0 ^1 ?5 H0 |9 Y# | 设置的波形控制模式:WAVE1 = 0x02,即产生三角波;4 M2 ^; Y t5 A

对于三角波的产生器,还有一段函数代码的作用是什么意思呢?

即其中的代码:6 h) Z' }$ e W# v0 ^1 s9 a

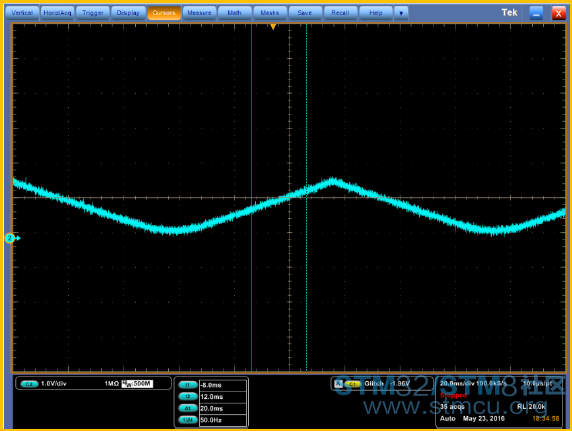

是什么作用呢? 产生的波形:/ N7 m0 i3 Y5 B0 f$ H

在加了函数之后:. W# A f3 e- B2 r$ F

从波形上来看,当参数数值不为0时,波形更像三角波,; t- a* v& E, W 那这个参数影响的是什么呢?

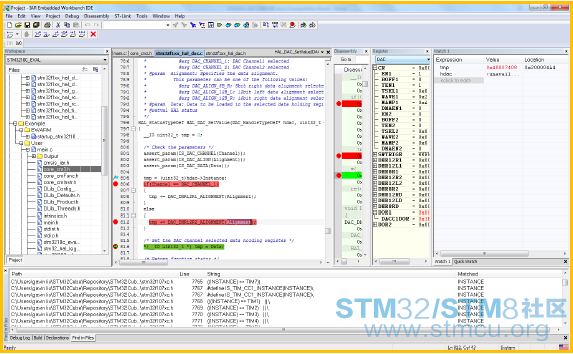

参数的tmp的值,位于0x200004A4处,初始值为0,运行到:

后tmp的值为0x40007400,该值是解释得通的:DAC外设的基地址(0x40007400)3 M" I; ?3 `- b3 L9 z

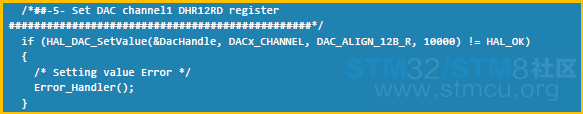

执行完语句之后:由于传递的参数是#define DAC_ALIGN_12B_R ((uint32_t)0x00000000) # V) G, W8 s) V q2 l( ~

得到的结果是(注意上图中虽然断点停在了DAC_DHR12R2_ALIGNMENT处,但是程序是DAC_CHANNEL_1,所以最终执行的还是下面的语句)* x# ~8 _ I5 @$ v$ m% t4 e

所以最终产生的效果就是:

地址为0x40007408的寄存器赋值,即下面寄存器赋值:

但是这寄存器的作用是什么呢?holding data?4 F0 s- F$ q: T1 s" b$ X: j Holding data寄存器,可以简单的理解为: 设置影响DAC的直流分量(直流分量还是根据下面的公式计算出来的):

当传递的参数设置为0是,DACoutput即三角波的最低电平为0: 当传递的参数设置为2047,DACoutput即三角波的最低电平为1.65V2 E8 i7 y1 L6 v4 l) |2 h

如果传递的参数设置为1024,DACoutput即三角波的最低电平为0.82V;/ _- C, L0 M( c6 j. j$ |. Q

如果传递的参数设置为3000,DACoutput即三角波的最低电平为2.42V;

5、噪声产生器 主要函数的代码如下:

9 G$ N0 _% n* r2 N' P, j6 A 由于一般的认为噪声是随机性的,所以可以认为只是修改幅值,对于其周期不可控 " G( P9 ~+ T6 K 文档下载地址: https://www.stmcu.org.cn/document/detail/index/id-2171391 S6 \! E: W" E; u3 u7 ]: Z/ I# T; X 2 t8 G8 y0 O* t1 N( i T) D 实战经验汇总:4 b5 e# |( u( u" N ` https://www.stmcu.org.cn/module/forum/thread-576401-1-1.html |

| 学习学习 |

,谢谢,学习一下! ,谢谢,学习一下! |

| 学习学习 |

楼主很棒呀 楼主很棒呀 |

| 谢谢,学习一下! |

| 谢谢发帖,辛苦!辛苦! |