|

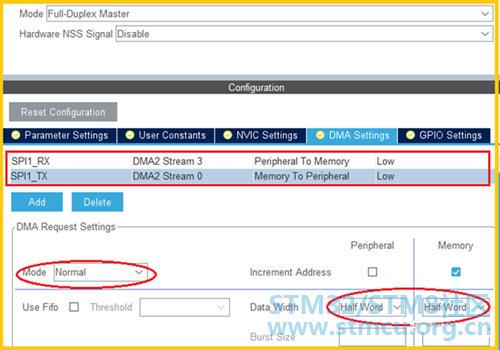

这里使用stm32h743-Nucleo板做个基于DMA传输的SPI收发应用示例。选择SPI1,MOSI与MISO短接,通过DMA自发自收,分开启Cache和不开启Cache来配置演示,以供参考。 ! m& `% ^7 B6 Q* N+ e3 K* A 利用STM32CubeMx进行配置,生成基于ARM MDK环境和Cube库的初始化代码。 0 } r- o) m# I2 ~2 h+ q SPI1配置在双工主角色,数据位设置为16位。开启SPI的TX/RX的DMA请求。

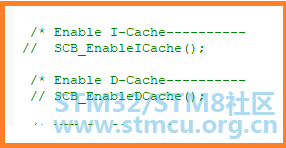

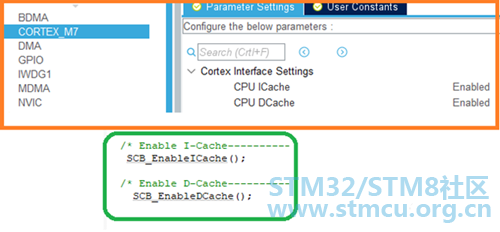

完成其它有关时钟、中断配置后,生成初始化代码并建立工程。 一、先不打开Cache。【屏蔽掉相关代码语句】 9 d/ u( G# D% ?) f7 w: z- {

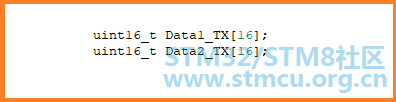

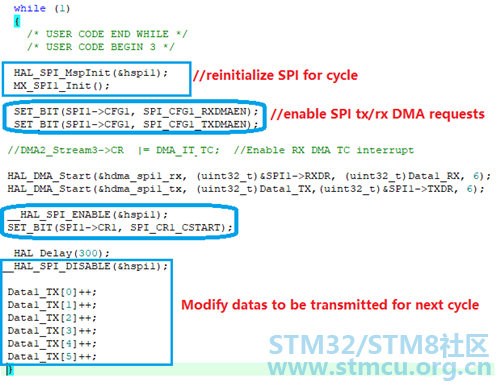

我在主程序里周期性地修改待发送的数据,并使能SPI及DMA传输进行数据收发。 6 V9 H$ n% ?: f' k" [' A' k 这里定义了两个内存数组用于数据的收发缓冲,分别是: 0 ]8 A; ^% ? M$ Z8 ?9 \

实验中我只各用到6个数据,并事先初始化。【对于验证而言,初始值是多少不重要】。 5 h1 [" F# J# i. ] J: Z5 E 添加相关用户代码。这里我没有开启DMA传输相关中断,这点可以根据需要开启。 4 |$ C8 i& z5 g

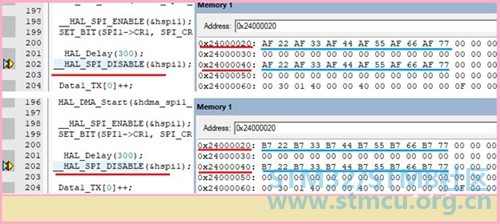

代码整理、调试完毕,看看结果。下面是通过打断点,在两个时刻的两幅截图。【注:接收缓冲区的起始地址为0x24000020,属于AXIM RAM区】。 # w+ m4 O' _) S

不难看出,收发数据很一致,那我们接下来看看使用Cache的情况。 二、开启Cache时的情况。 8 {. B# x, K( J6 O

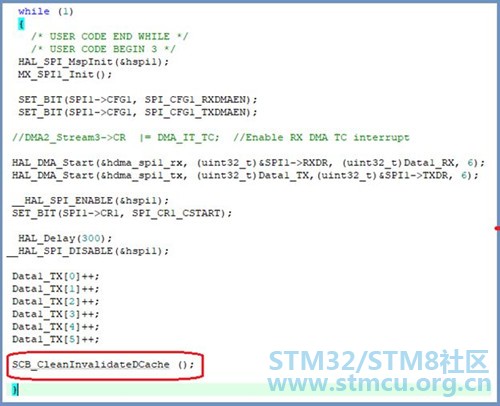

整个工作流程跟上面一样,在主程序里循环地触发SPI的DMA传输。因为开启了Cache,我们要注意数据一致性问题的处理。在主循环的修改发送收据操作后做了Dcache的清除和失效操作。当然,我们也可以开启DMA传输中断,比方在传输完成中断里做Cache相关的数据更新与维护操作。整个用户代码跟上面不开启Cache时几乎一样,就最后多了一句跟Cache相关的代码。

稍作整理、编译运行,看看结果。同样,下面是通过打断点,在两个时刻的两幅截图。【注:接收缓冲区起始地址是0x24000020,属于AXIM RAM区】。 + W- x/ g2 `/ Y' L& L& K

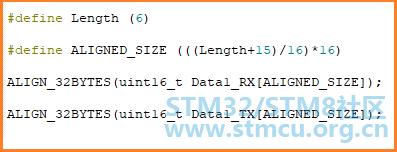

从验证结果可以看出,发送、接收的数据非常地一致。 这里提醒下,如果开启DCache,对于会被Cache的数据缓冲区,其地址以及缓冲区大小须遵循32字节对齐的原则。所以,关于收发缓冲区的定义及初始化,开启Cache时跟不开启Cache稍有点差异。【下面的6代表代码中用到的六个16位半字数据】 ) [+ ~+ H7 {1 l" b

好,整个示例就分享到这里,需要用到的代码都贴出来了。另外,当开启Cache之后,关于数据更新与维护我们也可以通过配置MPU来实现。 * x7 h5 H4 `$ `0 o2 r1 A ; i# ?7 ?8 @" g" G6 |' I8 I+ w |

【经验分享】STM32_H7_ADC

STM32H7R/S高性能MCU:安全性,大存储和优异图显赋能更多应用创新

Stm32H7XX GCC下分散加载实现

【银杏科技ARM+FPGA双核心应用】STM32H7系列10——ADC

DIY-STM32H750核心板

[nucleo-H7A3ZI-Q]1-点亮一个皮皮灯

DIY-STM32H743核心板

【银杏科技ARM+FPGA双核心应用】STM32H7系列57——MDK_FLM

1月10日有奖直播 | 基于STM32 的CODESYS智能自动化解决方案

STM32的CAN FD位定时设置注意事项