|

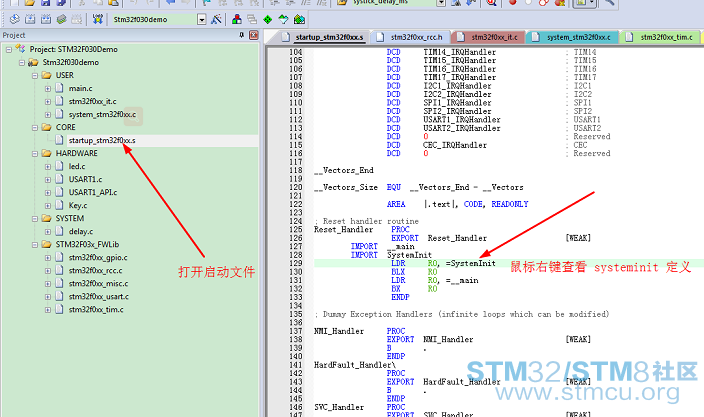

STM32F030F4P6单片机由外部时钟改为内部时钟的步骤 一.看程序运行的时候初始化时钟部分:

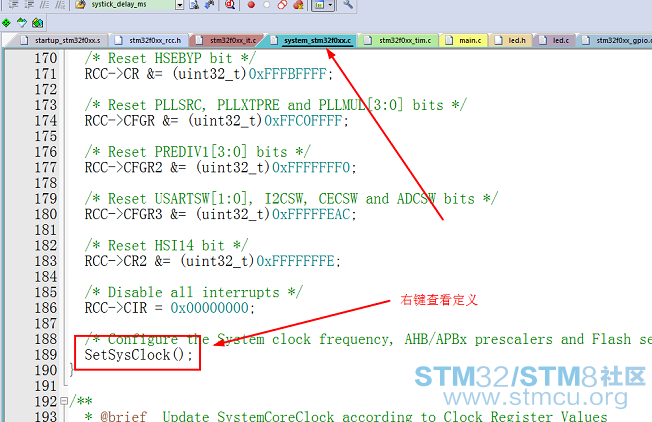

二.查看systeminit定义如下:

这就是打开的函数内容  这就是使用外部时钟的配置,也就是库函数的默认配置):static void SetSysClock(void) 这就是使用外部时钟的配置,也就是库函数的默认配置):static void SetSysClock(void){( w& L6 w! e+ k9 d __IO uint32_t StartUpCounter = 0, HSEStatus = 0;% f) m4 Y5 a- J1 i) b $ U x, ]- x6 r7 c /* SYSCLK, HCLK, PCLK configuration ----------------------------------------*/; h2 \0 O" C4 ~1 B$ s! f /* Enable HSE */ //打开外部时钟开关 RCC->CR |= ((uint32_t)RCC_CR_HSEON);2 `1 h( P5 \$ q% X5 R+ Z$ f /* Wait till HSE is ready and if Time out is reached exit *///判断外部时钟是否起振 do {; t, _" M# ~! g( m5 X- P5 [ HSEStatus = RCC->CR & RCC_CR_HSERDY;- o- I7 p# P8 V& o StartUpCounter++; } while((HSEStatus == 0) && (StartUpCounter != HSE_STARTUP_TIMEOUT)); J) Z. {& f0 t. A! R9 v3 F. R* ] if ((RCC->CR & RCC_CR_HSERDY) != RESET) {' A8 y- S1 q/ z5 [7 h8 N* B( F N HSEStatus = (uint32_t)0x01; } else { HSEStatus = (uint32_t)0x00; } , B$ s0 {" b* l+ H; [+ R& V if (HSEStatus == (uint32_t)0x01) {5 g8 N' n# v: r" t% T9 A1 r; R4 ^ /* Enable Prefetch Buffer and set Flash Latency */ //flash总线时钟使能% X0 ~+ i$ W' ~4 g. G: t' o# j( z FLASH->ACR = FLASH_ACR_PRFTBE | FLASH_ACR_LATENCY;: a5 T3 K4 J/ w( K# n /* HCLK = SYSCLK *///外设AHB总线时钟等于系统时钟7 M; S1 g- w/ q8 W RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1; ) f3 Z" M; d3 h4 V X- {" A' m M /* PCLK = HCLK *///外设APB总线时钟等于系统时钟5 I7 p) Q4 x$ x2 X* K RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE_DIV1; 8 q8 s. u; G; K4 O1 z4 n: L5 G# N- `& n /* PLL configuration = HSE * 6 = 48 MHz *///外部时钟6倍频 =系统时钟 RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLMULL)); RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_PREDIV1 | RCC_CFGR_PLLXTPRE_PREDIV1 | RCC_CFGR_PLLMULL6);' `2 H3 v: b0 I0 D7 \ " D) J4 M8 m Q /* Enable PLL *///使能锁相环倍频开关) c$ a' h# p8 Y1 l. @8 ~ RCC->CR |= RCC_CR_PLLON;) S/ |, N. N+ m& r( {- j /* Wait till PLL is ready *///等待锁相环就绪 while((RCC->CR & RCC_CR_PLLRDY) == 0)6 g+ c7 |* |* r/ g& q( _ { } /* Select PLL as system clock source *///选择锁相环输出时钟作为系统时钟 RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW)); RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL; 0 R- s) S; R4 |& o2 }. {+ ? , Q; n: s5 e! w) t* z9 ]( T /* Wait till PLL is used as system clock source *///等待锁相环输出时钟已经成为系统时钟# q2 \& D* D8 r$ ^/ W8 K; F while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)RCC_CFGR_SWS_PLL)5 R- o1 g5 [9 ]. U6 q, T" |( }/ g6 N { } }4 u; o/ R/ M" T4 M1 A else { /* If HSE fails to start-up, the application will have wrong clock configuration. User can add here some code to deal with this error */ } } 8 ~$ p P& V3 a3 {& ~. f+ a4 E 四.那么我们就按照上图的结构配置来修改SetSysClock()中的配置即可  采用内部RC时钟作为时钟源,蓝色字体为修改关键处): 采用内部RC时钟作为时钟源,蓝色字体为修改关键处):static void SetSysClock(void)- F0 A% O9 u; C! I8 Q4 W { __IO uint32_t StartUpCounter = 0, HSIStatus = 0; ; [9 j7 U8 [/ i4 l0 O /* SYSCLK, HCLK, PCLK configuration ----------------------------------------*/" s% R/ ?8 A7 M" G/ d: X /* Enable HSI*/ //使能内部时钟9 g4 ]+ ?/ g" L5 B RCC->CR |= ((uint32_t)RCC_CR_HSION;7 O1 \6 {! j/ W- G7 p! C2 A & K1 R9 B# S. V7 Z) }2 l /* Wait till HSI is ready and if Time out is reached exit */ //等待内部时钟起振 do {; D5 y& Q) }: o8 V8 S HSIStatus = RCC->CR & RCC_CR_HSIRDY; StartUpCounter++; } while((HSIStatus== 0) && (StartUpCounter != HSI_STARTUP_TIMEOUT)); if ((RCC->CR & RCC_CR_HSIRDY) != RESET)$ J) a* z) K* A {! i2 w5 Z% s! R) m# S1 {" T HSIStatus = (uint32_t)0x01; } else 1 D1 e0 ^1 W# S7 {, G$ ~8 r3 ~ {5 h4 p. ~2 d) ]6 t, C" x HSIStatus = (uint32_t)0x00;! H, Y5 X# E( R } if (HSIStatus == (uint32_t)0x01) { /* Enable Prefetch Buffer and set Flash Latency */ //flash总线时钟使能 FLASH->ACR = FLASH_ACR_PRFTBE | FLASH_ACR_LATENCY; ; C% M' X+ s8 E# r /* HCLK = SYSCLK *///外设AHB总线时钟等于系统时钟% ]' }# Z. N9 o) f, j RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;) z( z: x" W1 ^& E % N& ]! r: |5 m! \6 V- S /* PCLK = HCLK *///外设APB总线时钟等于系统时钟 RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE_DIV1; & A- ~) O, c" n# G2 c' r: n /* PLL configuration = HSI/2 * 12= 48 MHz */ RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLSRC | RCC_CFGR_PLLMULL)); RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSI_Div2 | RCC_CFGR_PLLMULL12); //RC时钟2分频后 进行12倍频</font>7 d2 }% ^& H$ W% Z" k' T /* Enable PLL *///使能锁相环倍频开关 RCC->CR |= RCC_CR_PLLON;- n! m! S3 c, C0 S E" S9 v$ @ ; _- j* e1 q# X0 T7 w /* Wait till PLL is ready *///等待锁相环就绪 while((RCC->CR & RCC_CR_PLLRDY) == 0)4 h" w; K0 ]* S6 X" ?% M { }- J ?0 g1 K1 O9 m5 k /* Select PLL as system clock source *///选择锁相环输出时钟作为系统时钟 ( t8 v) u7 w( n, ~ RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW)); RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL; ' u9 D+ L. i7 t7 S% ]3 J . Q. P, s, ]. Q4 c /* Wait till PLL is used as system clock source *///等待锁相环输出时钟已经成为系统时钟 while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)RCC_CFGR_SWS_PLL)/ h0 E; P; M* Q. f) U {9 l Q5 B8 q5 T9 t } }; K& }( G& S1 t- @ else3 x& `& e t0 Q* K3 W. k { /* If HSI fails to start-up, the application will have wrong clock ( K* ]/ J, {: I8 a" ]. B$ L configuration. User can add here some code to deal with this error */( O" t7 l& z) Z* L1 {! z# C & o* l6 h. u: }4 D* K } " c: U2 X. B4 i5 L8 ?1 R8 K }5 ?* Z! b t! c2 b( Y8 E( n . D' f& X& M: W# j! c3 W0 H, n 8 o; }( P7 `5 |$ e& z% P |

STM32固件库分享,超全系列整理

三创电子(Tcreate)-STM32F030核心板代码

STM32F0 ADC(DMA中断)多通道,注释超详细

FreeRTOS在STM32F030上的移植

基于STM32移植而引发的疑问经验分享

分享STM32F051中文参考手册(重制书签版)

游名:STM32F0+Trinamic智能步进驱动芯片TMC5160(最高20A)参考原...

【MCU实战经验】+STM32F030的步进电机加减速

STM32F0的中文技术参考手册(标签处理过)

基于STM32F030硬件SPI经验分享

点评

加超链确实有问题的,最好的方法是去格式在操作,会反馈给技术部门

好的!