SDRAM布线方法

1、无所谓在外面还是在内部,都可以,内外走线都要打孔。表层信号紧临地平面就不怕干扰,但要注意外表面空气介电常数不如隔绝空气的内部稳定,在一些湿度,温差大的地方的设备最好走内部,外部走地层,不过这样成本高。

2、等长不是目的,目的是满足建立保持时间,同频同相,采样正确。SDRAM是公共时钟模式,只关心建立时间,不关心保持时间。

1.SDRAM时钟信号:时钟信号频率较高,为避免传输线效应,按照工作频率达到或超过75MHz时布线长度应在1000mil以内的原则及为避免与相邻信号产生串扰,走线长度不超过1000mil,线宽10mil,内部间距5mil,外部间距30mil,要求差分布线,精确匹配差分对走线,误差允许在20mil以内。 2. 地址、片选及其它控制信号:线宽5mil,外部间距12mil,内部间距10mil,尽量走成菊花链拓补,可有效控制高次谐波干扰,可比时钟线长,但不能短。 3.SDRAM数据线:线宽5mil,内部间距5mil,外部间距8mil,尽量在同一层布线,数据线与时钟线的线长差控制在50mil内。 4.在重要的控制信号线上一搬串联33的电阻,消除干扰。

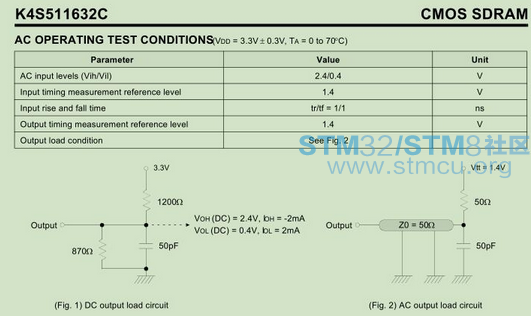

仔细查看SDRAM手册后发现一个图,如下

SDRAM数据引脚是50欧姆阻抗,我就用50欧姆阻抗的同轴线试试呗。 50欧姆的射频同轴电缆,5MM直径,感觉挺细了,拿到手还是感觉太粗。。。,凑合用吧。 把MCU和SDRAM之间的时钟线去掉,换成50欧姆同轴电缆,60M全SDRAM测试通过,90M,没问题,100M,没问题!

110M,仍然没问题;120M,也没问题;125M,又出错了。。。

这样的板子,SDRAM跑到120M,你还想怎样?还想怎样!。。。

SDRAM为系统二分频,此时,系统时钟为240M。。。。

单独测试GD32F450,可以稳定跑到250M,再高频率无法设置了,因为GD32F450倍频最高500,再二分频,最高就是250M。 附上工程文件吧,有需要的朋友拿去。 |  /3

/3